# Inter-Agency Workshop on HPC Resilience at Extreme Scale

National Security Agency Advanced Computing Systems February 21 – 24, 2012

### **Coordinating Representatives**

John Daly (DOD) Bill Harrod (DOE/SC) Thuc Hoang (DOE/NNSA) Lucy Nowell (DOE/SC)

## Workshop Report Committee

Bob Adolf (PNNL) Shekhar Borkar (Intel) Nathan DeBardeleben (LANL) Mootaz Elnozahy (IBM) Mike Heroux (Sandia) David Rogers (Sandia) Rob Ross (ANL) Vivek Sarkar (Rice U.) Martin Schulz (LLNL) Marc Snir (DOE/ANL) Paul Woodward (UMN)

> **Report Editor** John Daly (DOD)

### **Additional Workshop Participants**

Rob Aulwes (LANL) Marti Bancroft (MBC) Greg Bronevetsky (LLNL) Bill Carlson (IDA) Al Geist (ORNL) Mary Hall (U. Utah) Jeff Hollingsworth (UMD) Bob Lucas (USC/ISI) Andrew Lumsdaine (Indiana U.) Tina Macaluso (SAIC) Dan Quinlan (LLNL) Sonia Sachs (DOE/SC) John Shalf (LBNL) Tom Smith (DOD) Jon Stearley (Sandia) Bert Still (LLNL) Jon Wu (LBNL)

#### Abstract

The following report summarizes the proceedings of a three-and-a-half day inter-agency workshop focused on the technical challenges of HPC resilience in the 2020 Exascale timeframe. The resilience problem is not specific to any particular program or agency; coordinated resilience solutions will be challenging because of the need for a truly integrated approach. The interagency workshop therefore focused on articulating practical, synergetic R&D goals by assembling a small but diverse group of experts representing system hardware, system software, application developers and users, algorithms and libraries, file systems, I/O and storage, visualization and data analytics for a collective deep dive on the problem of resilience. The workshop format was highly interactive, focused on problem solving teams of not more than ten persons each. Participants were tasked to collaboratively develop a plan and roadmap for implementing resilience at extreme scale, resulting in "proof of concept" strategies for resilience on future, general purpose HPC systems in the application domains of "predictive science" and "not predictive science". Those strategies were analyzed in the context of future Exascale requirements relative to power. performance, reliability, usability, dependability and time-to-solution. That analysis consisted of an assessment of current capabilities, gaps and dependencies culminating in a strawman R&D roadmap for an integrated resilience framework. These outcomes demonstrate both the need for and existence of practical resilience strategies that address the future needs of applications within the constraints of future Exascale technology.

# **Executive Summary**

Resilience is about keeping the application workload running to a correct solution in a timely and efficient manner in spite of frequent hard (i.e., unrecoverable) and soft (i.e., recoverable) errors. At this inter-agency resilience workshop hosted by NSA Advanced Computing Systems, DOE/SC and DOE/NNSA, thirty representatives of DOD, DOE, the national labs, industry and academia came together to discuss the primary challenges facing resilience as we look down the road to general purpose HPC in the Exascale timeframe. Workshop participants identified the following topic areas as high priorities:

- Fault Characterization: Reliability will get worse with deeply scaled process technologies creating new modes of failure. Based on anticipated technology trends, the HPC community needs to develop a useful taxonomy for describing the types of faults that future systems are expected to encounter, including their anticipated frequency and impact.

- **Detection:** In the Exascale timeframe, error "recovery" will likely be manageable using known techniques for local checkpointing. Error "prediction" can reduce the frequency of permanent errors, not transients, but there are varying opinions on the current state of the research and whether or not the problem is solvable in the Exascale timeframe. The research focus should be error "detection" which requires the system and application to work together in a coordinated fashion. Industry is not going to solve this problem for the HPC community.

- **Fault-Tolerant Algorithms:** Three classes of algorithms were identified: (A) those that are embarrassingly fault-tolerant, (B) those that are not fault-tolerant but are self-checking and (C) those that are neither fault-tolerant nor self-checking. Most algorithms currently in class C above could be moved to class B or even class A through a moderate R&D investment.

- **Fault-Tolerant Programming Models:** Resilience would benefit strongly from a programming model that accommodates some notion of transactions in time (e.g., roll-back and recovery) and space (e.g., fault containment domains). An uncomplicated, directive-based interface using a handful of assertions (e.g., create persistent memory domains, allocate "reliable" and "unreliable" code regions, etc.) provides most of the necessary interfaces for implementing application fault-tolerance.

- **Fault-Tolerant System Services:** System software must be built hierarchically on a small set of highly trusted services. Techniques for fault-avoidance are known and used in critical systems, but come at a higher development and execution cost. The software stack should be structured to utilize the majority of application and system execution cycles in software that may occasionally fail and rely on trusted services to recover.

- **Tools:** Resilience lacks a mature, validated test infrastructure to verify the effectiveness of various resilience strategies for keeping the application running in the face of high rates of hard and soft errors. Fault injection tools are particularly needed to simulate all classes of faults. Models will be required to support the fault testing infrastructure at scale. In addition, tools themselves will need their own resilience strategy to operate correctly at scale.

In summary, the number of errors, particularly soft errors, occurring on HPC systems will continue to increase. A right-sized and well-conceived resilience strategy in the Exascale timeframe will be ultimately far more cost effective for HPC than continuing to rely on ad-hoc resilience solutions. That strategy must at a minimum provide for a resilience infrastructure that facilitates (1) system management of hard errors, by effectively "converting" them to soft errors whenever feasible, and (2) application management of soft errors, through interfaces that allow it simple controls over how and when to respond to errors. Such a framework, based on timely and coordinated error detection and recovery, can serve as the foundation of a deployable and sustainable HPC resilience strategy in the Exascale timeframe.

# Contents

| 1.1    Motivation for the Workshop    1      1.1.1    Hardware Considerations    1      1.1.2    Software Considerations    1      1.1.3    The Role of System Scale    1      1.1.3    The Role of System Scale    1      1.2.1    Vision for the Workshop    2      1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2.4    Productivity Performance and Reliability Tradeoffs    6      2.2.3    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for New Approaches    7      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs <t< th=""><th>1</th><th>Intr</th><th>oduction 1</th></t<>                                                              | 1 | Intr | oduction 1                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------------------------------------------------------|

| 1.1.1    Hardware Considerations    1      1.1.2    Software Considerations    1      1.1.3    The Role of System Scale    1      1.2    Vision for the Workshop    2      1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2.4    Pulpication Challenges    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.3.3    The Need for Portability    6      2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience from A                                                                                                          |   | 1.1  | Motivation for the Workshop                            |

| 1.1.3    The Role of System Scale    1      1.2    Vision for the Workshop    2      1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2    Application Challenges    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Software    10                                                                                                                              |   |      | 1.1.1 Hardware Considerations                          |

| 1.1.3    The Role of System Scale    1      1.2    Vision for the Workshop    2      1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2.4    Application Challenges    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Software    10      3.2.3    System Imact of Faults    9 </td <td></td> <td></td> <td>1.1.2 Software Considerations</td>                                                        |   |      | 1.1.2 Software Considerations                          |

| 1.2    Vision for the Workshop    2      1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges of HPC Resilience at Extreme Scale    3      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2.4    Application Challenges    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1.1    Categorization of Faults    10                                                                                     |   |      |                                                        |

| 1.2.1    The Nature of the Challenge    2      1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges .    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1.2    Expected Impact of Faults    10                                                                                            |   | 1.2  |                                                        |

| 1.2.2    Workshop Structure    2      2    Technical Challenges of HPC Resilience at Extreme Scale    3      2.1    System Challenges    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2    Application Challenges    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.3.3    The Need for Portability    6      2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1    System Hardware    9      3.1.2    Expected Impact of Faults    10      3.2    System Software                                                                                                                |   |      | 1                                                      |

| 2.1    System Challenges    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.2    Why Not Just Build More Reliable Systems?    5      2.1.4    Current Approaches    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.3.3    The Need for Portability    6      2.3.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.1    Idempotence an                                                                                                          |   |      |                                                        |

| 2.1    System Challenges    4      2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.2    Why Not Just Build More Reliable Systems?    5      2.1.4    Current Approaches    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.3.3    The Need for Portability    6      2.3.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.1    Idempotence an                                                                                                          | 2 | Tec  | nnical Challenges of HPC Resilience at Extreme Scale 3 |

| 2.1.1    Description of Hardware and Software    4      2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture .    5      2.2    Application Challenges .    5      2.2.1    Current Approaches .    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable .    6      2.2.3    The Need for Portability .    6      2.2.4    Productivity, Performance and Reliability Tradeoffs .    6      2.3.1    The Need for New Approaches .    7      2.3.2    The Impact of Soft Errors .    7      2.3.3    New Opportunities in Hardware .    8      2.3.4    Global View of Resilience .    8      2.3.5    Evaluating the Tradeoffs .    8      3    Perspectives on HPC Resilience from Across the System Stack .    9      3.1.1    Categorization of Faults .    10      3.2    System Mardware .    10      3.2    System Software .    10      3.2    System Software .    10      3.2.1    Idempotence and Data-Flow Tasks .    10      3.2.2    The Run                                                                                                          |   |      |                                                        |

| 2.1.2    Why Not Just Build More Reliable Systems?    4      2.1.3    A Resilient Software Architecture    5      2.2    Application Challenges    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.4    Inle Meed for New Approaches    7      2.3.5    Evaluating the Tradeoffs    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Hardware    9      3.1.1    Categorization of Faults    10      3.2    System Software    10      3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3.1    Current Practices    12                                                                                                                                               |   |      |                                                        |

| 2.1.3 A Resilient Software Architecture .    5      2.2 Application Challenges .    5      2.2.1 Current Approaches .    5      2.2.2 The Importance of Understanding What Is and Is Not Reliable .    6      2.2.3 The Need for Portability .    6      2.2.4 Productivity, Performance and Reliability Tradeoffs .    6      2.3 Resilience Challenges .    6      2.3.1 The Need for New Approaches .    7      2.3.2 The Impact of Soft Errors .    7      2.3.3 New Opportunities in Hardware .    8      2.3.4 Global View of Resilience .    8      2.3.5 Evaluating the Tradeoffs .    8      3 Perspectives on HPC Resilience from Across the System Stack .    9      3.1.1 Categorization of Faults .    9      3.1.2 Expected Impact of Faults .    10      3.2 System Software .    10      3.2.1 Idempotence and Data-Flow Tasks .    10      3.2.2 The Runtime and Compiler .    12      3.3.1 Current Practices .    12      3.3.2 Significant Changes at the Exascale .    13      3.3.3 Assumptions and Requirements .    13      3.3.4 Need for a Coordinated System Approach .    13      3.4 Data Storage and I/O .    1 |   |      |                                                        |

| 2.2    Application Challenges    5      2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Hardware    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2 <td< td=""><td></td><td></td><td></td></td<>                                                                                                                     |   |      |                                                        |

| 2.2.1    Current Approaches    5      2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3    Resilience Challenges    6      2.3    Resilience Challenges    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Hardware    9    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2 <td></td> <td>22</td> <td></td>                                                                                                                                   |   | 22   |                                                        |

| 2.2.2    The Importance of Understanding What Is and Is Not Reliable    6      2.2.3    The Need for Portability    6      2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3    Resilience Challenges    6      2.3    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Mardware    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2.3    System Software    10      3.2.4    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3.4    Need for a Coordinated System Approach    13      3.4    Need for a Coordinated System Approach    13      3.4    Data Storage and I/O    14      3.4.1    Current Trends    14                                                                                                                                                           |   | 2.2  |                                                        |

| 2.2.3The Need for Portability62.2.4Productivity, Performance and Reliability Tradeoffs62.3Resilience Challenges62.3.1The Need for New Approaches72.3.2The Impact of Soft Errors72.3.3New Opportunities in Hardware82.3.4Global View of Resilience82.3.5Evaluating the Tradeoffs82.3.5Evaluating the Tradeoffs93.1Categorization of Faults93.1.1Categorization of Faults93.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.3Visualization and Data Analytics123.3Areas of Greatest Concern123.3Assumptions and Requirements133.4Need for a Coordinated System Approach133.4Nead for a Coordinated System Approach143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                                        |

| 2.2.4    Productivity, Performance and Reliability Tradeoffs    6      2.3    Resilience Challenges    6      2.3.1    The Need for New Approaches    7      2.3.2    The Impact of Soft Errors    7      2.3.3    New Opportunities in Hardware    8      2.3.4    Global View of Resilience    8      2.3.5    Evaluating the Tradeoffs    8      3.1    System Hardware    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3.1    Current Practices    12      3.3.1    Current Practices    12      3.3.3    Assumptions and Requirements    13      3.4    Need for a Coordinated System Approach    13      3.4    Data Storage and I/O    14      3.4.1    Current Trends    14                                                                                                                                                                                                                                                                        |   |      |                                                        |

| 2.3 Resilience Challenges    6      2.3.1 The Need for New Approaches    7      2.3.2 The Impact of Soft Errors    7      2.3.3 New Opportunities in Hardware    8      2.3.4 Global View of Resilience    8      2.3.5 Evaluating the Tradeoffs    8      3.1 System Hardware    9      3.1.1 Categorization of Faults    9      3.1.2 Expected Impact of Faults    10      3.2.3 Visualization and Data-Flow Tasks    10      3.2.2 The Runtime and Compiler    11      3.2.3 Areas of Greatest Concern    12      3.3.1 Current Practices    12      3.3.3 Assumptions and Requirements    13      3.4 Need for a Coordinated System Approach    13      3.4 Data Storage and I/O    14      3.4.1 Current Trends    14                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                        |

| 2.3.1The Need for New Approaches72.3.2The Impact of Soft Errors72.3.3New Opportunities in Hardware82.3.4Global View of Resilience82.3.5Evaluating the Tradeoffs82.3.5Evaluating the Tradeoffs83Perspectives on HPC Resilience from Across the System Stack93.1System Hardware93.1.1Categorization of Faults93.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.3Visualization and Data Analytics123.3.1Current Practices123.3.2Significant Changes at the Exascale123.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 0.9  |                                                        |

| 2.3.2The Impact of Soft Errors72.3.3New Opportunities in Hardware82.3.4Global View of Resilience82.3.5Evaluating the Tradeoffs83.1System Hardware93.1.1Categorization of Faults93.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.3Visualization and Data Analytics123.3.1Current Practices123.3.2Significant Changes at the Exascale133.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 2.3  |                                                        |

| 2.3.3 New Opportunities in Hardware82.3.4 Global View of Resilience82.3.5 Evaluating the Tradeoffs82.3.5 Evaluating the Tradeoffs83 Perspectives on HPC Resilience from Across the System Stack93.1 System Hardware93.1.1 Categorization of Faults93.1.2 Expected Impact of Faults103.2 System Software103.2.1 Idempotence and Data-Flow Tasks103.2.2 The Runtime and Compiler113.2.3 Areas of Greatest Concern123.3 Visualization and Data Analytics123.3.1 Current Practices123.3.2 Significant Changes at the Exascale123.3.4 Need for a Coordinated System Approach133.4 Data Storage and I/O143.4.1 Current Trends143.4.2 Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                        |

| 2.3.4Global View of Resilience82.3.5Evaluating the Tradeoffs83Perspectives on HPC Resilience from Across the System Stack93.1System Hardware93.1.1Categorization of Faults93.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.4Visualization and Data Analytics123.3Significant Changes at the Exascale123.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 1                                                      |

| 2.3.5    Evaluating the Tradeoffs    8      3    Perspectives on HPC Resilience from Across the System Stack    9      3.1    System Hardware    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    9      3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2    Significant Changes at the Exascale    12      3.3.3    Assumptions and Requirements    13      3.4    Data Storage and I/O    14      3.4.1    Current Trends    14                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                                        |

| 3 Perspectives on HPC Resilience from Across the System Stack    9      3.1 System Hardware    9      3.1.1 Categorization of Faults    9      3.1.2 Expected Impact of Faults    10      3.2 System Software    10      3.2.1 Idempotence and Data-Flow Tasks    10      3.2.2 The Runtime and Compiler    11      3.2.3 Areas of Greatest Concern    12      3.3 Visualization and Data Analytics    12      3.3.1 Current Practices    12      3.3.2 Significant Changes at the Exascale    12      3.3.4 Need for a Coordinated System Approach    13      3.4 Data Storage and I/O    14      3.4.1 Current Trends    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |                                                        |

| 3.1    System Hardware    9      3.1.1    Categorization of Faults    9      3.1.2    Expected Impact of Faults    10      3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    11      3.2.3    Areas of Greatest Concern    12      3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2    Significant Changes at the Exascale    12      3.3.3    Assumptions and Requirements    13      3.4    Need for a Coordinated System Approach    14      3.4.1    Current Trends    14      3.4.2    Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 2.3.5 Evaluating the Tradeoffs                         |

| 3.1.1Categorization of Faults93.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.3Visualization and Data Analytics123.3.1Current Practices123.3.2Significant Changes at the Exascale123.3.3Assumptions and Requirements133.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 | Per  |                                                        |

| 3.1.2Expected Impact of Faults103.2System Software103.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.4Visualization and Data Analytics123.3Significant Changes at the Exascale123.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 3.1  |                                                        |

| 3.2    System Software    10      3.2.1    Idempotence and Data-Flow Tasks    10      3.2.2    The Runtime and Compiler    10      3.2.3    Areas of Greatest Concern    11      3.2.3    Areas of Greatest Concern    12      3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2    Significant Changes at the Exascale    12      3.3.3    Assumptions and Requirements    13      3.4    Need for a Coordinated System Approach    13      3.4.1    Current Trends    14      3.4.2    Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |                                                        |

| 3.2.1Idempotence and Data-Flow Tasks103.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.3Visualization and Data Analytics123.3.1Current Practices123.3.2Significant Changes at the Exascale123.3.3Assumptions and Requirements133.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 3.1.2 Expected Impact of Faults                        |

| 3.2.2The Runtime and Compiler113.2.3Areas of Greatest Concern123.3Visualization and Data Analytics123.3.1Current Practices123.3.2Significant Changes at the Exascale123.3.3Assumptions and Requirements133.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 3.2  | System Software                                        |

| 3.2.3 Areas of Greatest Concern123.3 Visualization and Data Analytics123.3.1 Current Practices123.3.2 Significant Changes at the Exascale123.3.3 Assumptions and Requirements133.4 Need for a Coordinated System Approach133.4 Data Storage and I/O143.4.1 Current Trends143.4.2 Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 3.2.1 Idempotence and Data-Flow Tasks                  |

| 3.3    Visualization and Data Analytics    12      3.3.1    Current Practices    12      3.3.2    Significant Changes at the Exascale    12      3.3.3    Assumptions and Requirements    13      3.3.4    Need for a Coordinated System Approach    13      3.4    Data Storage and I/O    14      3.4.1    Current Trends    14      3.4.2    Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | 3.2.2 The Runtime and Compiler                         |

| 3.3.1Current Practices123.3.2Significant Changes at the Exascale123.3.3Assumptions and Requirements133.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 3.2.3 Areas of Greatest Concern                        |

| 3.3.2Significant Changes at the Exascale123.3.3Assumptions and Requirements133.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.3  | Visualization and Data Analytics                       |

| 3.3.3Assumptions and Requirements133.3.4Need for a Coordinated System Approach133.4Data Storage and I/O143.4.1Current Trends143.4.2Software Concerns14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | 3.3.1 Current Practices                                |

| 3.3.4    Need for a Coordinated System Approach    13      3.4    Data Storage and I/O    14      3.4.1    Current Trends    14      3.4.2    Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 3.3.2 Significant Changes at the Exascale 12           |

| 3.4 Data Storage and I/O    14      3.4.1 Current Trends    14      3.4.2 Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 3.3.3 Assumptions and Requirements                     |

| 3.4.1    Current Trends    14      3.4.2    Software Concerns    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 3.3.4 Need for a Coordinated System Approach           |

| 3.4.2 Software Concerns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.4  | Data Storage and I/O                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 3.4.1 Current Trends                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 3.4.2 Software Concerns                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                                        |

| 3.4.4 The Role of Abstractions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |                                                        |

| 3.5 Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 3.5  |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 3.5.1 Enhancing Existing Tools                         |

| 2.5.1 Enhancing Existing Teola                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | <b>5.5.1</b> Emitancing Existing 100Is                 |

|   |     | 3.5.2          | Tools for Fault Monitoring, Management, and Logging                                                         |

|---|-----|----------------|-------------------------------------------------------------------------------------------------------------|

|   |     | 3.5.3          | The Need for Interface to Introspect Resilience Techniques                                                  |

|   |     | 3.5.4          | Fault Tolerance in Tools                                                                                    |

|   |     | 3.5.5          | System Support for Tools                                                                                    |

|   |     | 3.5.6          | Testing Through Fault Injection Tools                                                                       |

|   | 3.6 |                | ithms                                                                                                       |

|   | 0.0 | 3.6.1          | Background                                                                                                  |

|   |     | 3.6.2          | Persistent Local Data                                                                                       |

|   |     | 3.6.3          | Algorithm-based Self-consistency Checking                                                                   |

|   |     | 3.6.4          | Selective Reliability                                                                                       |

|   | 3.7 |                | cation Developers and Users                                                                                 |

|   | 5.1 | 3.7.1          |                                                                                                             |

|   |     |                | *                                                                                                           |

|   |     | 3.7.2          | Alternatives to Global Checkpoint Restart                                                                   |

|   |     | 3.7.3          | Recovering State After an Interrupt 20                                                                      |

|   |     | 3.7.4          | Implications of Resilience                                                                                  |

|   |     | 3.7.5          | Coordinated Resilience: An Example                                                                          |

|   |     | 3.7.6          | Role of the Application in a Total Resilience Strategy 22                                                   |

| 4 | Dot | olonin         | g an HPC Resilience Framework for Extreme Scale 23                                                          |

| - | 4.1 |                | nt State                                                                                                    |

|   | 1.1 | 4.1.1          | Hardware Features                                                                                           |

|   |     | 4.1.2          | Reactive Response                                                                                           |

|   |     | 4.1.2          | Proactive Screening                                                                                         |

|   |     | 4.1.3          |                                                                                                             |

|   |     | 4.1.4<br>4.1.5 | State Storage (i.e., Check-Pointing)24Architectural Considerations24                                        |

|   |     |                |                                                                                                             |

|   | 4.0 | 4.1.6          | Proxy Applications                                                                                          |

|   | 4.2 | -              | $ \begin{array}{c} \dots \\ \dots $ |

|   |     | 4.2.1          | The Need to Better Understand the Problem to be Solved                                                      |

|   |     | 4.2.2          | Support for Event Analysis and Notification                                                                 |

|   |     | 4.2.3          | Coordinated Holistic Approach                                                                               |

|   |     | 4.2.4          | Viable Prediction 28                                                                                        |

|   |     | 4.2.5          | Adoption and the Road to It                                                                                 |

|   | 4.3 | Depen          | adencies                                                                                                    |

|   |     | 4.3.1          | Fault Model 29                                                                                              |

|   |     | 4.3.2          | Fault Notification 30                                                                                       |

|   |     | 4.3.3          | Containment Domains                                                                                         |

|   |     | 4.3.4          | Fault Characterization 30                                                                                   |

|   | 4.4 | Strate         | gy                                                                                                          |

|   |     | 4.4.1          | Focus on Real Application Requirements                                                                      |

|   |     | 4.4.2          | Transactional Semantics                                                                                     |

|   |     | 4.4.3          | Error Containment                                                                                           |

|   |     | 4.4.4          | Efficiency and Overhead                                                                                     |

|   |     | 4.4.5          | Flexible Tradeoffs                                                                                          |

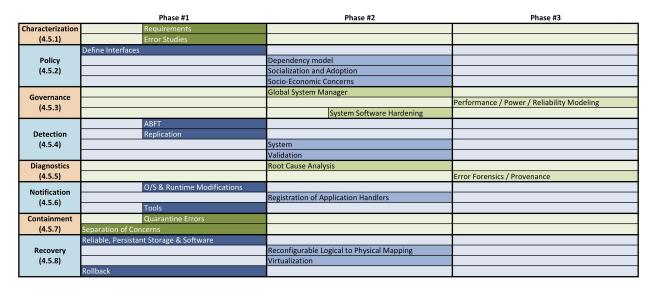

|   | 4.5 | Roadr          | nap                                                                                                         |

|   |     | 4.5.1          | Characterization                                                                                            |

|   |     | 4.5.2          | Resilience Policy                                                                                           |

|   |     | 4.5.3          | Governance Mechanisms / Framework                                                                           |

|   |     | 4.5.4          | Detection (i.e., Something Happened)                                                                        |

|   |     |                | $\langle \rangle$                                                                                           |

|   |       | 4.5.5 | Diagnostics (i.e., What Happened?)                | 37 |

|---|-------|-------|---------------------------------------------------|----|

|   |       | 4.5.6 | Notification                                      | 38 |

|   |       | 4.5.7 | Containment                                       | 38 |

|   |       | 4.5.8 | Recovery                                          | 38 |

| 5 | Sun   | nmary | and Conclusions 4                                 | 40 |

|   | 5.1   | Scope | of the Challenge                                  | 40 |

|   |       | 5.1.1 | Building on Success                               | 40 |

|   |       | 5.1.2 | An Overarching Strategy to Address the Challenges | 41 |

|   |       | 5.1.3 | Cultural Hurdles in the Commodity Space           | 42 |

|   | 5.2   | Final | Recommendations                                   | 42 |

| R | efere | nces  | 2                                                 | 46 |

# 1 Introduction

# 1.1 Motivation for the Workshop

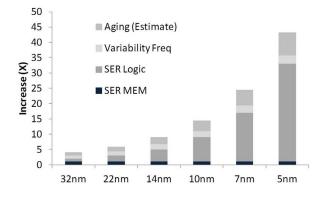

Resilience is about keeping the application workload running to a correct solution in a timely and efficient manner in spite of system failures. Future extreme scale supercomputers are likely to suffer more frequent failures than current systems: As devices scale, they are more susceptible to upsets due to radiation and to errors due to manufacturing variances. The probability of multiple bit upsets is growing, since an event is increasingly likely to impact multiple nearby cells. The use of near-threshold voltage in order to reduce power consumption also increases error rates. Thus, we can expect more frequent hardware failures, and a significant rate of undetected soft errors.

# 1.1.1 Hardware Considerations

Techniques do exist to develop more reliable hardware components – but such techniques have a cost, and this cost will increase. It is far from obvious that the commodity market will provide cheap, highly reliable components that can be used in future supercomputers. Components with lower reliability will be cheaper and will be "good enough" for most markets such as personal and mobile computing and large clouds. The market niches that require highly reliable systems – e.g., financial transactions or critical systems – will pay an increasing price premium for high reliability or will learn how to build highly reliable systems from unreliable components. This "low-end disruption" [8] has already started, with a large price differential between high volume commodity processors and "mainframe quality" servers.

# 1.1.2 Software Considerations

In addition, supercomputing software is becoming more complex. This software serves a narrow market and is hard to test at scale; hence, it is reasonable to assume it has a higher defect rate than similar commercial software, and is more failure-prone. Indeed, a large fraction of failures in current supercomputers is due to failures in the parallel file system and other complex software subsystems. Additionally, the application is becoming more dependent on multiple levels of the software stack including libraries and the runtime to support resilience. An error that kills the communications library kills the applications depending on it, whether or not the actual error was in fact "fatal" to the application.

# 1.1.3 The Role of System Scale

The HPC community appears to be learning how to cope with increasing failure rates and, quite possibly, with a high incidence of undetected soft errors. Our current systems are not ready for such a change. As an example, in a system where global checkpoint and restart take 20 minutes, and where a component fails once an hour, more than 60% of the system time would be spent checkpointing and restarting [9]. Faster checkpointing (e.g., using non-volatile memory) would help, but would come at a nontrivial cost; faster checkpointing would also increase the likelihood that errors occurring before checkpointing would be detected only after checkpointing. Finally, none of the currently used techniques handle undetected soft errors.

*Resilience at Extreme Scale* (RES) is the problem of designing extreme scale supercomputers that provide useful answers with acceptable time and power consumption, from hardware and software components that are failure-prone. This is a cross-cutting problem: Errors in hardware can corrupt application data, application code, system data or system code. Detection of and

recovery from errors may happen at different layers of the system stack, with different costs and different implications to hardware and software designers; recovery is likely to require a coordinated action of many of these layers.

On the other hand, research on resilience is very compartmentalized: Research on resilient hardware assumes that error detection and/or correction is fully contained at the hardware level; research on resilient algorithms focus on application data corruptions but ignore any other type of errors; etc. A piecemeal approach will not produce a solution to the resilience problem at extreme scale. Instead, the HPC community needs to take a global view of the problem and on the possible ways of handling detection and correction in a coordinated manner, at different levels of the system.

### 1.2 Vision for the Workshop

The Inter-Agency Workshop on HPC Resilience at Extreme Scale, that took place at the Center for Exceptional Computing, Catonsville, MD, February 21-24, 2012 brought together a small group of experts from multiple disciplines to start developing this roadmap and a strategy for R&D that will lead to timely solutions to the RES challenge. The workshop was not intended to be the last word in resilience, nor was it intended to exhaust the resilience challenges in the Exascale timeframe. Rather, the vision for the workshop was to demonstrate both the necessity and sufficiency of a coordinated resilience strategy. We hope that the results reported here can serve as a "stake in the ground", a useful first attempt to define a practical resilience framework for the Exascale timeframe.

#### 1.2.1 The Nature of the Challenge

The RES problem matters to mission agencies – in particular DOD and DOE. Its solution will come from an R&D program coordinated across multiple agencies. Such a program needs to be informed by a proposed roadmap toward RES, an identification of the main roadblocks, and a focused list of problems that need to be solved. Solutions can be incremental, encompassing an increasing number of applications and reducing, over time, the human effort needed to achieve RES.

Thus, attendees were chosen to span the RES space as broadly as possible while still keeping the working group sizes manageable (ten people or fewer) and the discussions focused. Participants were instructed to concentrate on requirements, not existing solutions. They were explicitly told that their current research interests were "off limits" for discussion. Participants stepped through the process of articulating a cogent RES strategy and asked to distinguish "what needs to be done" from "what could be done" or what constitutes an "interesting" research question.

#### 1.2.2 Workshop Structure

The format of this report reflects the overall structure of the workshop. The technical challenges of resilience in the Exascale timeframe, described in Section 2, were addressed first via a series of overview talks. Next, domain experts were asked to summarize their requirements and capabilities with regards to resilience: what they need from resilience and what they themselves can provide. These discussions are summarized in Section 3.

Working from their knowledge of the salient architectural features of the system hardware and software, working groups developed an actual implementation that integrates target application domains into a notional system stack. Working groups were given tasking and specific assignments focused around developing a resilience framework for the Exascale timeframe, summarized in Section 4. They were encouraged to avoid getting "stuck" on issues not resolvable within the scope of the workshop, but to press on towards developing a credible resilience plan for the Exascale timeframe based on the knowledge of the experts at hand. This report describes their results.

# 2 Technical Challenges of HPC Resilience at Extreme Scale

The challenges of resilience in the Exascale timeframe are well documented by the HPC community through a variety of Exascale studies and plans such as [6, 11]. For the purpose of this workshop we summarize the key points as follows:

- The scale challenge: At the system level, horizontal scaling of technology will require three orders of magnitude increase in the number or size of components to reach Exascale. The resulting aggregated failure rate at the system level will be two to three orders of magnitude higher than today's systems, assuming the component level reliability is kept at today's FIT rates. Some experts even doubt that maintaining today's FIT rates will be possible without an increase in power consumption, challenging the constraints on energy usage further for an Exascale system. It is therefore reasonable to expect that an Exascale system will have much shorter MTBF than existing Petascale systems.