#### COMP 322: Fundamentals of Parallel Programming

#### Lecture 16: Point-to-Point Synchronization with Phasers

Zoran Budimlić and Mack Joyner {zoran, mjoyner}@rice.edu

http://comp322.rice.edu

#### Worksheet 15: Data Driven Futures

| Name: | Netid: |

|-------|--------|

|-------|--------|

For the example below, will reordering the five async statements change the meaning of the program (assuming that the semantics of the reader/writer methods depends only on their parameters)? If so, show two orderings that exhibit different behaviors. If not, explain why not.

No, reordering the asyncs doesn't change the meaning of the program. Regardless of the order, Task 3 will always wait on Task 1. Task 5 will always wait on Task 2. Task 4 will always wait on both Task 1 and 2.

```

DataDrivenFuture left = new DataDrivenFuture();

DataDrivenFuture right = new DataDrivenFuture();

finish {

async await(left) leftReader(left); // Task3

async await(right) rightReader(right); // Task5

async await(left,right)

bothReader(left,right); // Task4

async left.put(leftWriter()); // Task1

async right.put(rightWriter()); // Task2

}

```

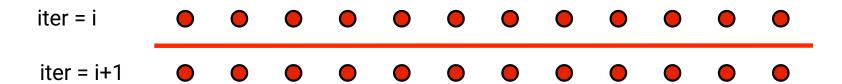

## Barrier vs Point-to-Point Synchronization in One-Dimensional Iterative Averaging Example

Barrier synchronization

Question: when can the point-to-point computation graph result in a smaller CPL than the barrier computation graph?

Answer: when there is variability in the node execution times.

# Phasers: a unified construct for barrier and point-to-point synchronization

- HJ phasers unify barriers with point-to-point synchronization

- Inspiration for java.util.concurrent.Phaser

- Previous example motivated the need for "point-to-point" synchronization

- With barriers, phase i of a task waits for all tasks associated with the same barrier to complete phase i-1

- With phasers, phase i of a task can select a subset of tasks to wait for

- Phaser properties

- —Support for barrier and point-to-point synchronization

- —Support for dynamic parallelism the ability for tasks to drop phaser registrations on termination (end), and for new tasks to add phaser registrations (async phased)

- A task may be registered on multiple phasers in different modes

#### Simple Example with Four Async Tasks and One Phaser

```

finish (() -> {

1.

ph = newPhaser(SIG WAIT); // mode is SIG WAIT

2.

asyncPhased(ph.inMode(SIG), () -> {

3.

// A1 (SIG mode)

4.

doA1Phase1(); next(); doA1Phase2(); });

5.

asyncPhased(ph.inMode(SIG_WAIT), () -> {

6.

// A2 (SIG WAIT mode)

7.

doA2Phase1(); next(); doA2Phase2(); });

8.

asyncPhased(ph.inMode(HjPhaserMode.SIG WAIT), () -> {

9.

10.

// A3 (SIG WAIT mode)

doA3Phase1(); next(); doA3Phase2(); });

11.

asyncPhased(ph.inMode(HjPhaserMode.WAIT), () -> {

12.

13.

// A4 (WAIT mode)

doA4Phase1(); next(); doA4Phase2(); });

14.

});

15.

```

### Computation Graph Schema Simple Example with Four Async Tasks and One Phaser

#### Semantics of next depends on registration mode

SIG\_WAIT: next = signal + wait

SIG: next = signal WAIT: next = wait

# SIG SIG\_WAIT SIG\_WAIT WAIT A<sub>1</sub> A<sub>2</sub> A<sub>3</sub> A<sub>4</sub> signal next

#### Summary of Phaser Construct

- Phaser allocation

- HjPhaser ph = newPhaser(mode);

- Phaser ph is allocated with registration mode

- Phaser lifetime is limited to scope of Immediately Enclosing Finish (IEF)

- Registration Modes

- HjPhaserMode.SIG, HjPhaserMode.WAIT,

HjPhaserMode.SIG\_WAIT, HjPhaserMode.SIG\_WAIT\_SINGLE

- NOTE: phaser WAIT is unrelated to Java wait/notify (which we will study later)

- Phaser registration

- asyncPhased (ph<sub>1</sub>.inMode(<mode<sub>1</sub>>), ph<sub>2</sub>.inMode(<mode<sub>2</sub>>), ... () -> <stmt> )

- Spawned task is registered with ph<sub>1</sub> in mode<sub>1</sub>, ph<sub>2</sub> in mode<sub>2</sub>, ...

- Child task's capabilities must be subset of parent's

- asyncPhased <stmt> propagates all of parent's phaser registrations to child

- Synchronization

- next();

- Advance each phaser that current task is registered on to its next phase

- Semantics depends on registration mode

- Barrier is a special case of phaser, which is why next is used for both

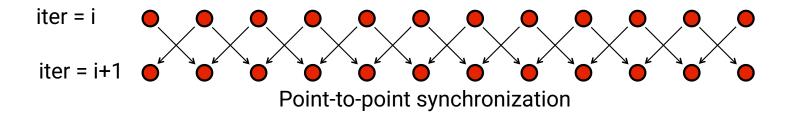

#### Capability Hierarchy

A task can be registered in one of four modes with respect to a phaser:

SIG\_WAIT\_SINGLE, SIG\_WAIT, SIG, or WAIT. The mode defines the set of capabilities —

signal, wait, single — that the task has with respect to the phaser. The subset relationship

defines a natural hierarchy of the registration modes. A task can drop (but not add)

capabilities after initialization.

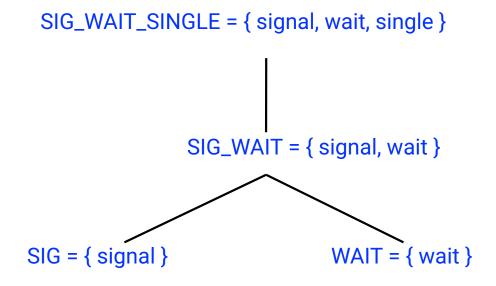

#### Left-Right Neighbor Synchronization (with m=3 tasks)

```

1. finish(() -> { // Task-0

final HjPhaser ph1 = newPhaser(SIG WAIT);

2.

3.

final HjPhaser ph2 = newPhaser(SIG WAIT);

final HiPhaser ph3 = newPhaser(SIG WAIT);

4.

asyncPhased(ph1.inMode(SIG),ph2.inMode(WAIT),

5.

6.

() -> { doPhase1(1);

next(); // signals ph1, waits on ph2

7.

doPhase2(1);

8.

9.

}); // Task T1

asyncPhased(ph2.inMode(SIG),ph1.inMode(WAIT),ph3.inMode(WAIT),

10.

11.

() -> { doPhase1(2);

12.

next(); // signals ph2, waits on ph1 and ph3

13.

doPhase2(2);

14.

}); // Task T2

15.

asyncPhased(ph3.inMode(SIG),ph2.inMode(WAIT),

16.

() -> { doPhase1(3):

next(); // signals ph3, waits on ph2

17.

18.

doPhase2(3);

19.

}); // Task T3

20.}); // finish

```

## Computation Graph for m=3 example (without async-finish nodes and edges)

#### forallPhased barrier is just an implicit phaser!

```

1. forallPhased(iLo, iHi, (i) -> {

2. S1; next(); S2; next();{...}

3. });

is equivalent to

1. finish(() -> {

2. // Implicit phaser for forall barrier

final HjPhaser ph = newPhaser(SIG_WAIT);

forseq(iLo, iHi, (i) -> {

5.

asyncPhased(ph.inMode(SIG_WAIT), () -> {

6.

S1; next(); S2; next();{...}

}); // next statements in async refer to ph

8. });

```

#### Midterm exam (Exam 1)

- Midterm exam (Exam 1) will be held during COMP 322 lab time at 4pm on Thursday, February 21, 2019

- Closed-notes, closed-book, written exam scheduled for 2.5 hours during 4pm 6:30pm (but you can leave early if you're done early!)

- The exam will be in Canvas AND on paper. You are allowed to use your laptop ONLY to enter your answers in Canvas, nothing else

- Scope of exam is limited to Lectures 1 16 (all topics in Module 1 handout)

- Since this is a written exam and not a programming assignment, syntactic errors in program text will not be penalized (e.g., missing semicolons, incorrect spelling of keywords, etc) so long as the meaning of your solution is unambiguous.

- If you believe there is any ambiguity or inconsistency in a question, you should state the ambiguity or inconsistency that you see, as well as any assumptions that you make to resolve it.

- We will have a recap of Lectures 1-16 on Monday, February 18th, and an interactive Q&A session on Wednesday, February 20th.

# Worksheet #16a: Left-Right Neighbor Synchronization using Phasers (turn the page over for the Worksheet #16b)

| Name:  |                            | i=1 | i=2 | i=3 | i=4 | i=5 | i=6 | i=7 | i=8 |

|--------|----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Nume.  | doPhase1(i)                | •   |     | •   |     |     |     |     |     |

| Netid: | doPhase1(i)<br>doPhase2(i) |     |     |     |     |     |     |     |     |

Complete the phased clause below to implement the point-to-point synchronization shown above for m tasks (generalization of slide 9)

```

1. finish (() -> {

final HiPhaser[] ph =

new HjPhaser[m+2]; // array of phaser objects

forseq(0, m+1, (i) -> { ph[i] = newPhaser(SIG_WAIT) });

forseq(1, m, (i) -> {

5.

asyncPhased(

ph[i-1].inMode(....),

ph[i].inMode(....),

ph[i+1].inMode(....), ()->{

6.

doPhase1(i);

7.

next();

doPhase2(i); }); // asyncPhased

}); // forseq

10.}); // finish

```

# Worksheet #16b: Reordered Asyncs with One Phaser (turn the page over for Worksheet #16a)

Task A4 has been moved up to line 6. Does this change the computation graph in slide 5? If so, draw the new computation graph. If not, explain why the computation graph is the same.

```

1. finish (() -> {

2.

ph = newPhaser(SIG_WAIT); // mode is SIG_WAIT

asyncPhased(ph.inMode(SIG), () -> {

3.

// A1 (SIG mode)

4.

5.

doA1Phase1(); next(); doA1Phase2(); });

asyncPhased(ph.inMode(HjPhaserMode.WAIT), () -> {

6.

7.

// A4 (WAIT mode)

doA4Phase1(); next(); doA4Phase2(); });

8.

9.

asyncPhased(ph.inMode(SIG_WAIT), () -> {

// A2 (SIG_WAIT mode)

10.

doA2Phase1(); next(); doA2Phase2(); });

11.

12.

asyncPhased(ph.inMode(HjPhaserMode.SIG WAIT), () -> {

13.

// A3 (SIG WAIT mode)

14.

doA3Phase1(); next(); doA3Phase2(); });

15.

});

```

#### **BACKUP SLIDES START HERE**