#### RICE UNIVERSITY

# Optimizing Convolutions in State-of-the-art Convolutional Neural Networks on Intel Xeon Phi

by

#### Ankush Mandal

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

Master of Science

APPROVED, THESIS COMMITTEE:

Vivek Saekar

Vivek Sarkar, Chair

Professor of Computer Science

E.D. Butcher Chair in Engineering

Rajkishore Barik

Research Scientist, Intel Labs

Anshumali Shrivastava

Assistant Professor of Computer Science

Keith D. Cooper

L. John and Ann H. Doerr Professor in

Computational Engineering

Houston, Texas

July, 2017

#### ABSTRACT

Optimizing Convolutions in State-of-the-art Convolutional Neural Networks on Intel Xeon Phi

by

#### Ankush Mandal

Convolution layers are the core of Convolutional Neural Networks (CNNs), a class of Deep Neural Networks which provide state-of-the-art results in pattern recognition tasks in various domains, such as image recognition, speech recognition, and natural language processing. However, CNNs are very time consuming to train due to the computationally intensive nature of convolution operation. As a result, we have a prolific number of optimized implementations of convolution using matrix-matrix multiplication formulation, FFT formulation, Winograd algorithm, and direct convolution. Interestingly, most of these implementations target GPU architecture, which is mainly due to - 1) higher theoretical peak FLOPs of GPU and 2) popularity of CUDA deep learning library. However, not much investigation has been done on the performance of convolution on high-end CPUs such as Intel second generation Xeon Phi, codenamed Knights Landing (KNL) with theoretical peak performance of 6 TFLOPS. So, here we shed some light on what we can achieve regarding performance for convolution on these high-end CPUs. In this work, we optimize directed convolution for Intel Xeon Phi systems with AVX-512 support. Our strategy involves dynamic compilation approach along with standard compiler optimizations and software prefetching. We show that our JIT-based approach for direct convolution achieves close to peak performance on KNL for many cases. We also analyze

the performance of convolution layers of several state-of-the-art CNNs, pointing out what helps in performance gain and what breaks our approach.

# Acknowledgments

First and foremost, I would like to convey my deepest gratitude to my advisor Dr. Vivek Sarkar for his mentorship, encouragement, and support throughout my graduate study at Rice University. His guidance and enthusiasm in research were invaluable to my development as a graduate student. He has been my source of inspiration whenever I faced difficulties. I owe him so much for giving me the opportunity to join Habanero Extreme Scale Software Research Group.

I would like to express the greatest degree of appreciation to my committee member Dr. Rajkishore Barik for giving me the opportunity to work with him at Intel. His expertise and insights were indispensable to the success of this project. I am incredibly grateful for his unwavering support during my time at Intel. I would also thank the team at Intel for all the help in this work.

I would like to thank my committee members Dr. Anshumali Shrivastava and Dr. Keith Cooper for their time and valuable feedbacks on this thesis.

I am grateful to all the members of the Habanero Extreme Scale Software Research group for their help and feedback in my research work. My study at Rice would not have been as entertaining and educational without them.

I have been very fortunate to have great friends in my graduate life. I am very thankful for all their support and encouragement. Special thanks to Ananya, Arijit, Arkabandhu, Arunim, Debarshi, Hamim, Himadri, Nilanjan, Pranabendu, Prasanth, Puspita, Rabimba, Rohan, Ronnie, Sagnik, Saikat, Sandip, Shams, Shantanu, Shuvadeep, Siam, Souray, Sriraj, Trijit.

Last but not the least, I am indebted to my parents Kalpana Mandal and Durgapada Mandal, and my sister Ankita Mandal for their unconditional love. They continuously supported and encouraged me to pursue my dreams. Without them standing by my side, I could not have come this far.

# Contents

|          | Abs  | tract       |                                                      | i  |

|----------|------|-------------|------------------------------------------------------|----|

|          | Ack  | nowledg     | gments                                               | iv |

|          | List | of Illus    | strations                                            | vi |

|          | List | of Tab      | les                                                  | ix |

| 1        | Int  | roduo       | ction                                                | 1  |

| <b>2</b> | Ba   | ckgro       | und                                                  | 4  |

|          | 2.1  | Convo       | olution                                              | 4  |

|          | 2.2  | Intel 2     | Xeon Phi systems                                     | 6  |

|          | 2.3  | LIBX        | SMM JITer                                            | 8  |

| 3        | Op   | ${f timiz}$ | ations for Direct Convolution on KNL                 | 9  |

|          | 3.1  | Naive       | Direct Convolution for Back Propagation              | 10 |

|          | 3.2  | Naive       | Direct Convolution for Weight Update                 | 10 |

|          | 3.3  | Data        | Layout                                               | 11 |

|          | 3.4  | Optin       | nized Direct Convolution for Back Propagation on KNL | 14 |

|          |      | 3.4.1       | Vectorization                                        | 14 |

|          |      | 3.4.2       | Optimize for Temporal and Spatial Locality           | 15 |

|          |      | 3.4.3       | Optimize loads and stores                            | 18 |

|          |      | 3.4.4       | Runtime Code Specialization and Parallelization      | 21 |

|          |      | 3.4.5       | Optimize Code Size                                   | 24 |

|          |      | 3.4.6       | Hiding fmadd Latency                                 | 25 |

|          |      | 3.4.7       | Software Prefetch                                    | 26 |

|          |      | 3.4.8       | Low Precision Operations                             | 27 |

|          |      | 3.4.9       | Packed fmadd Operations                              | 30 |

|   | 3.5 | Optin  | nized Direct Convolution for Weight Update on KNL | 32 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 3.5.1  | Vectorization                                     | 32 |

|   |     | 3.5.2  | Optimize for Temporal and Spatial Locality        | 33 |

|   |     | 3.5.3  | Optimize loads and stores                         | 33 |

|   |     | 3.5.4  | Runtime Code Specialization and Parallelization   | 36 |

|   |     | 3.5.5  | Software Prefetch                                 | 36 |

| 4 | Per | rform  | ance Results on KNL                               | 39 |

| 5 | Re  | lated  | Work                                              | 56 |

|   | 5.1 | GEMI   | M Based Approach                                  | 56 |

|   | 5.2 | Convo  | olution on GPUs                                   | 57 |

|   | 5.3 | Convo  | olution on Other Hardware Accelerators            | 57 |

|   | 5.4 | Convo  | olution on CPUs                                   | 57 |

|   | 5.5 | JIT B  | ased Approach                                     | 58 |

|   | 5.6 | Distri | buted CNN Training                                | 58 |

| 6 | Co  | nclus  | ion and Future Work                               | 59 |

|   | Bil | oliogr | aphy                                              | 61 |

# Illustrations

| 2.1  | Depiction of convolution (adapted from [1])                             | 5  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | KNL Architecture (adapted from $[2]$ )                                  | 6  |

|      |                                                                         |    |

| 3.1  | Pseudo code of naive direct convolution for back propagation            | 10 |

| 3.2  | Pseudo code of naive direct convolution for weight update               | 11 |

| 3.3  | Pictorial representation of input tensor                                | 12 |

| 3.4  | Pseudo code for back propagation after vectorization                    | 16 |

| 3.5  | Pseudo code for back propagation after 1-D register blocking            | 17 |

| 3.6  | Pseudo code for back propagation after L1 cache blocking                | 19 |

| 3.7  | Access pattern for input when stride is 1                               | 20 |

| 3.8  | Pseudo code for back propagation after optimization of loads and stores | 22 |

| 3.9  | Pseudo code for back propagation after runtime code specialization      |    |

|      | and parallelization                                                     | 23 |

| 3.10 | Pseudo code for back propagation with JIT interface and software        |    |

|      | prefetching                                                             | 27 |

| 3.11 | Low precision FMA strategy                                              | 31 |

| 3.12 | Pseudo code of naive direct convolution for weight update               | 32 |

| 3.13 | Pseudo code for weight update after vectorization                       | 33 |

| 3.14 | Pseudo code for weight update after 2-D register blocking and cache     |    |

|      | blocking                                                                | 34 |

| 3.15 | Pseudo code for weight update after optimizing loads and stores         | 35 |

| 3.16 | Pseudo code for weight update after runtime code specialization and     |    |

|      | parallelization                                                         | 37 |

| 3.17 | Pseudo code for weight update with software prefetching                 | 38 |

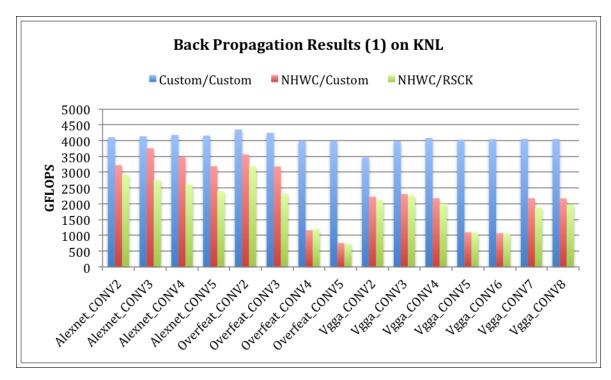

| 4.1 | Performance results for Back Propagation on AlexNet, Overfeat, and   |    |

|-----|----------------------------------------------------------------------|----|

|     | Vgga                                                                 | 46 |

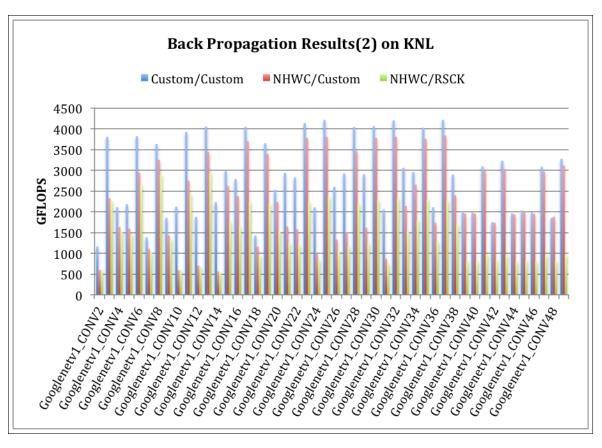

| 4.2 | Performance results for Back Propagation on GoogleNetV1              | 47 |

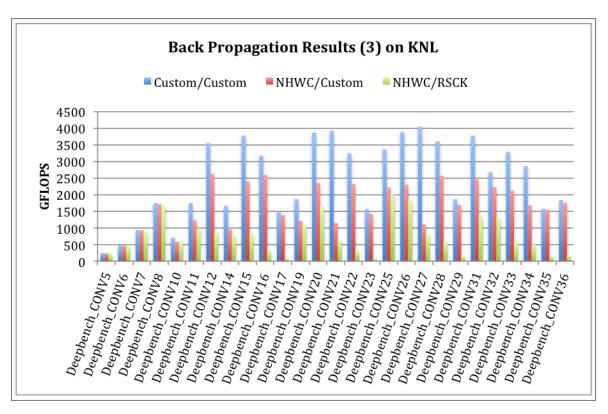

| 4.3 | Performance results for Back Propagation on DeepBench                | 49 |

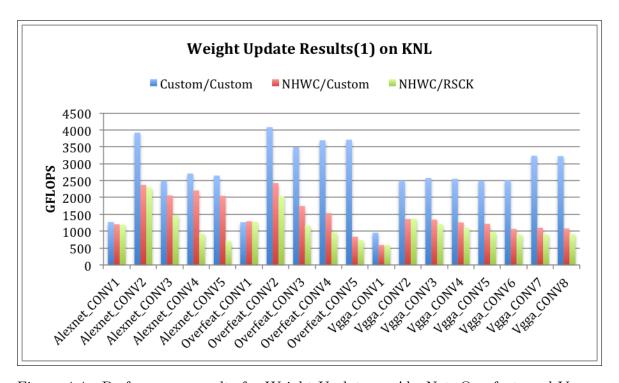

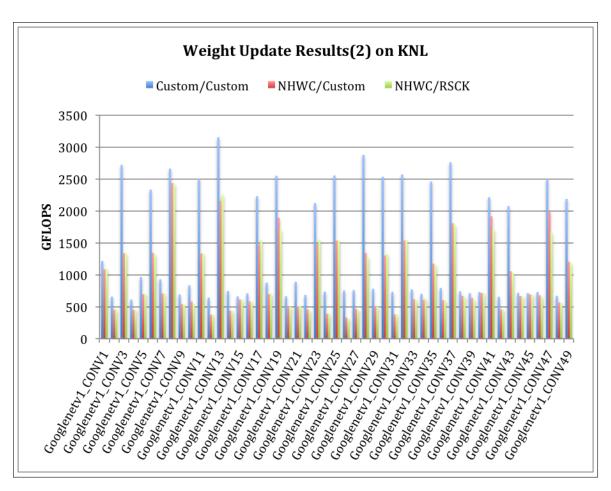

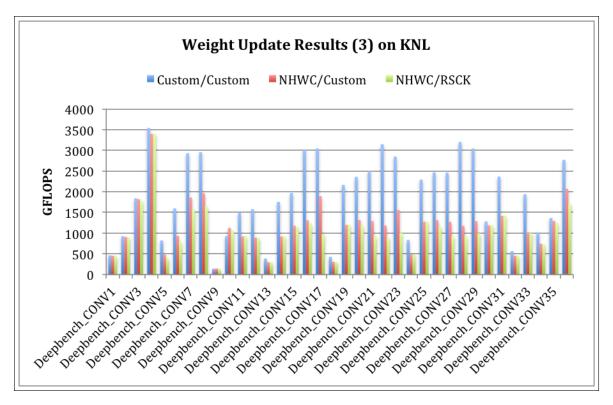

| 4.4 | Performance results for Weight Update on AlexNet, Overfeat, and Vgga | 49 |

| 4.5 | Performance results for Weight Update on GoogleNetV1                 | 50 |

| 4.6 | Performance results for Weight Update on DeepBench                   | 51 |

# Tables

| 3.1 | Tensor Dimensions                                                  | 12 |

|-----|--------------------------------------------------------------------|----|

|     |                                                                    |    |

| 4.1 | Parameters for Convolutional Layers of AlexNet, Overfeat, and Vgga | 40 |

| 4.2 | Parameters for Convolutional Layers of GoogleNetV1                 | 41 |

| 4.3 | Parameters for Convolutional Layers of DeepBench                   | 43 |

| 4.4 | Back Propagation: Base Line Comparison                             | 52 |

| 4.5 | Weight Update: Base Line Comparison                                | 53 |

| 4.6 | Back Propagation: GEMM Method Comparison                           | 54 |

| 4.7 | Weight Update: GEMM Method Comparison                              | 55 |

# Chapter 1

#### Introduction

Concepts from the field of Machine Learning drive many aspects of the modern society, from social networks to recommendations on e-commerce, and becoming more and more commercially valuable as we see an increasing number of consumer products powered by them such as cameras, self-driving car. In particular, Deep Learning has become one of the most critical technologies, demonstrating equal or even better than human-level performance for tasks in domains of object recognition, board games, and speech recognition. This became possible because due to two reasons - 1) its underlying model, Deep Neural Network (DNN) can learn features automatically from large datasets and represent complex functions using multiple hidden layers, 2) recent advances in processor technologies made it possible to satisfy the huge computational requirement associated with Deep Learning. Naturally, it is now an active topic of research in the community, leading many academic groups and companies release open source frameworks aiming to improve the productivity of data scientists by abstracting away implementation details. TensorFlow [3], Caffe [4] are few popular ones among such frameworks.

Although Different DNNs aim at different problems, one of the most important application today is image recognition [5] and currently, Convolution Neural Network (CNN) is the state-of-the-art DNN for this. The core of a CNN consists of multiple layers performing a large number of small convolutions. As an abundant amount of data parallelism is available in the computation of convolution through many images or mini-batch size and feature maps or channels, massively parallel architectures such

as GPUs, in particular, has been used for training and inference on CNNs. As a consequence, all existing frameworks [3, 6, 7, 8, 4, 9] have GPU backend that implements convolution layers as libraries using cuDNN. However, high-end CPUs such as second-generation Intel Xeon Phi systems [10] with 70+ cores and AVX-512 support, has not been explored much in the domain of CNN. So in our perspective, it is noteworthy to shed some light on CPU performance and understand what it takes to achieve peak performance on CPUs for CNNs.

Although training and inference on CNNs are both time-consuming operations, requiring high-performance software implementations, training, in particular, takes an enormous amount of time and can span several weeks. For example, AlphaGo [11] took three weeks and 340 million training steps on 50 GPUs. So, we investigate into what makes training on CNN so time-consuming. We discover two factors here 1) training involves back propagation and weight update whereas inference does not, and it is much harder to have an optimized implementation for back propagation and weight update compared to forward propagation, a step common to both training and inference 2) usually training is done for large number of iterations compared to inference which is done in single pass. As the back propagation and weight update code are used over so many times during training, it makes sense to put some effort to optimize these steps.

Regarding convolution method, a general approach is to flatten the corresponding input data (image2column operation) and use standard matrix multiplications (GEMM) on the flattened data. This approach has a severe drawback. The flattening of input data is done to represent the image data as a 2-D matrix so that convolution can be formulated as GEMM. Hence, flattening step copies the input data from image data format (i.e. [Number of Images][Channel][Height][Width]) to 2-D matrix format, which is very low on arithmetic operations and makes the step purely memory

bandwidth bound. Even though the GEMM computation is highly optimized, the flattening step acts as a bottleneck and creates a huge performance penalty. In recent years, a new and straightforward approach for implementation of convolution has started to materialize, called direct convolution. In this method, convolution is directly applied to input data.

In this work, we try to optimize back propagation and weight update on secondgeneration Intel Xeon Phi systems. We leverage direct convolution approach to avoid

expensive memory operations and implement the convolutions associated with back

propagation and weight update as direct convolution. [12] has shown that statically

tuned BLAS calls incur overheads for small GEMMs and therefore do not achieve

peak performance. They propose to use runtime code specialization via a JIT for

small GEMMs. Since the tensor dimensions vary widely for convolutions on CNNs,

we also propose runtime code specialization through a similar JIT strategy. We lay

our data in a data format that helps the computation and apply standard compiler

optimizations such as register blocking, cache blocking. When we mention "data

format", we mean a particular sequence of the tensor dimensions. We also perform

some optimizations specific to Xeon Phi, such as software prefetching. We demonstrate that, for training steps on CNNs, peak performance can be achieved on CPUs

targeting High-Performance Computing (HPC) using this approach.

# Chapter 2

# Background

In this section, we describe the computation, i.e. convolution, and the architecture on which we are trying to optimize the computation, i.e. second-generation Intel Xeon Phi systems.

#### 2.1 Convolution

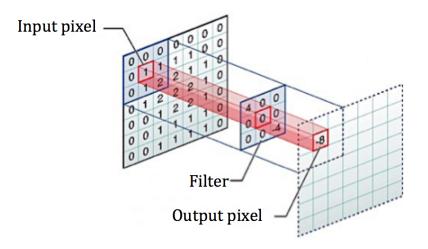

In a convolution layer, each output pixel is generated from the weighted sum of a spatially connected neighborhood of input. So, convolution operation adds each element of the input image with elements from a defined neighborhood after multiplying all the elements with specific weights from filter data as shown in Figure 2.1.

In case of CNNs, we usually perform convolution over a batch of images. This is termed as batched convolution [13]. Mathematically, a batched convolution deals with three four-dimensional tensors:  $I \in \mathbb{R}^{NCHW}$  as input image data,  $O \in \mathbb{R}^{NKPQ}$  as output data, and  $F \in \mathbb{R}^{KCRS}$  as filter data. The input data ranges over N images in a mini-batch, C input image feature maps, H rows or image height, W columns or image width. The filter data ranges over K output feature maps, C input feature maps, C rows or filter height, and C columns or filter width. The height and width of the output tensor is function of input image and filter height and width along with padding and stride, i.e.  $P = f(H, R, stride_h, pad_h)$ , and  $Q = f(W, S, stride_w, pad_w)$ . Here  $stride_h$  and  $stride_w$  are stride of access along respectively input image height and input image width.  $pad_h$  and  $pad_w$  are respectively height and width of the zero padding on each side of the input image. The

Figure 2.1: Depiction of convolution (adapted from [1])

function f is defined as follows:

$$f(H, R, stride\_h, pad\_h) = \left\lceil \frac{H - R + 1 + 2 * pad\_h}{stride\_h} \right\rceil$$

(2.1)

Now, the convolution for back propagation can be defined as follows:

For  $\forall n \in [0, N), \forall c \in [0, C), \forall h \in [0, H), and \forall w \in [0, W),$

$$I[n, c, h, w] = \sum_{k=0}^{K} \sum_{r=0}^{R} \sum_{s=0}^{S} F[k, c, r, s].O[n, k, g(h, r, stride\_h, pad\_h),$$

$$g(w, s, stride\_w, pad\_w)]$$

(2.2)

Similarly, the convolution for weight update can be defined as follows:

For

$$\forall k \in [0, K)$$

,  $\forall c \in [0, C)$ ,  $\forall r \in [0, R)$ , and  $\forall s \in [0, S)$ ,

$$F[k, c, r, s] = \sum_{n=0}^{N} \sum_{p=0}^{P} \sum_{q=0}^{Q} I[n, c, p * stride\_h + r, q * stride\_w + s].O[n, k, p, q] \quad (2.3)$$

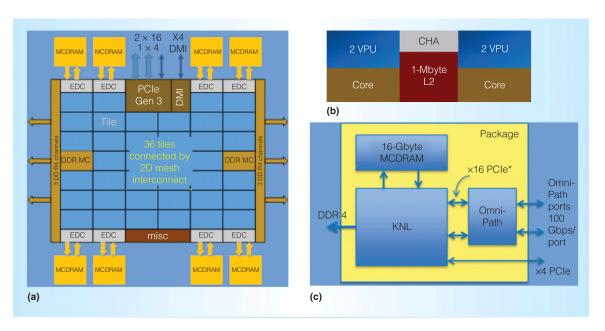

Figure 2.2: KNL Architecture (adapted from [2])

## 2.2 Intel Xeon Phi systems

As discussed in chapter 1, we are interested in investigating what peak performance can be achieved on CPUs for convolutions in back propagation and weight update. As we are dealing with performance critical application, we are interested in high-end CPUs targeting HPC. Intel Xeon Phi processors are one family of such CPUs. The second generation Intel Xeon Phi processor code-named Knights Landing (KNL) is one of the strongest general purpose CPUs available today. So, we choose this processor as target architecture for our implementation and evaluate our implementation concerning performance over this processor.

A sample figure representing the architectural overview of KNL chip is given in Figure 2.2. The KNL chip features up to 72 out-of-order Silvermont Atom cores with each being 4-way hyper-threaded to hide memory and multi-cycle instruction latency. The cores are tiled in pairs and connected via 2-D mesh interconnect. In general, it is advisable to set one core aside for OS housekeeping. Micro-architecture

wise, one key feature of this processor is that each core is embedded with two 512-bit vector processing units (VPU) for increased SIMD level parallelism, i.e. each core can start execution of two 16-wide single precision SIMD instructions in the same clock cycle. Besides this, each core has 32 KB L1 data cache (3 cycles latency), 32 KB L1 instruction cache (3 cycles latency). Each tile has 1MB globally coherent L2 cache (17 cycle latency) shared between two cores. Apart from standard DDR4 memory up to 384 GB with a bandwidth of 90 GB/s, an additional 16 GB of high bandwidth stacked MCDRAM can be attached to the system that provides 500GB/s memory bandwidth. The latency for accessing data from memory can be as high as 160 ns. Another important feature of KNL is that it supports explicit cache operation hint instructions. These include instructions to prefetch data into L1 or L2 caches (via prefetcht0 and prefetcht2 instructions respectively) and instruction modes to reduce the priority of a cache line. These instructions work together with streaming hardware L2 cache prefetcher. To achieve peak performance, one needs to carefully architect the placement and amount of L1/L2 prefetch instructions within the application. It is important to mention that the machine is only two-issue wide but features two VPUs per core, which results in an upper limit of achievable peak performance as 80%of the theoretical peak performance. The reason behind this is the fact that, to achieve theoretical peak FLOPs, two issues have to be always filled with vector instructions of floating point operations. This is not possible in reality because there are overhead of loop management, pointer address calculations, and software prefetching to support corresponding memory movement operations. All of these instructions fill at least one of two pipeline slots and block a useful FMA instruction. Therefore, to achieve optimal performance on this system, these instructions should be limited to a bare minimum, which requires high-quality code concerning optimizations and can be quite a bit of challenge.

#### 2.3 LIBXSMM JITer

We have previously mentioned in chapter 1 that we adopt a runtime code specialization strategy by using JIT compilation. In our work, we use LIBXSMM SMALL-GEMM JITer [12] for generating optimized code for direct convolution at runtime. Originally, the JITer is designed for small matrix multiplications. It has an application specific GEMM code generation backend. Using this assembly generator for JITing, it showed significant performance improvement on x86 architectures. In order to generate code for direct convolution using this JITer, we modified the assembly generator backend. The reasons behind choosing this JITer are:

- 1) It is very light weight; it adds very little overhead during JITing. By compromising on generality, this JITer generates problem specific codes at runtime very efficiently. As we are targeting a particular problem, i.e. direct convolution, it makes sense to use a fast and low profile JITer. LIBXSMM SMALLGEMM JITer fits this criterion exactly.

- 2) It is designed for small matrix multiplication which follows fused multiply add pattern. As our direct convolution problem also follows fused multiply add pattern, this JITer is a good fit for our problem.

- 2) It targets AVX-512 systems, specifically Intel Xeon Phi systems. As our target is KNL, extending the AVX-512 code generation for direct convolution on KNL is easier.

We discuss in detail in section 3.4.4 about how we use this JITer and which goals we try to achieve during code generation.

# Chapter 3

# Optimizations for Direct Convolution on KNL

The input parameters for convolution including N, C, H, W, R, S, u or  $stride\_h$ , and v or  $stride\_w$  (section 2.1) vary significantly across layers of a CNN and also across different CNNs. This makes it hard to achieve peak IA performance by static compilation because the optimization factors and strategy depend on these parameters and these parameters are only known during execution time. For example, the loops to tile and their tiling factor, the loops to unroll and their unroll factor cannot be determined statically without knowing the values of these parameters. In order to address this problem, we propose a runtime code specialization approach to produce optimized code at runtime depending on the values of these parameters. This makes the core of our ninja code for direct convolution on IA.

In this section, we first discuss the nave direct convolution in back propagation and weight update. Then we discuss the data layouts for input, output, and weight tensors we considered and how they impact code optimization. We also give details on how we can efficiently implement direct convolution for back propagation and weight update on x86 architectures. For these ninja implementations, we discuss in particular about compiler optimizations such as register blocking, tiling, and unrolling to optimize the corresponding loop nests, runtime code specialization, code quality enhancements, and software prefetching.

```

1 for(img = 0; img < N; ++img) { //independent</pre>

for(ifm = 0; ifm < C; ++ifm) { //independent</pre>

for(ofm = 0; ofm < K; ++ofm) { //reduction</pre>

for (oj = 0; oj < P; ++oj) { //carry dependency}

ij = oj * u;

6

for (oi = 0; oi < Q; ++oi) { //carry dependency

ii = oi * v;

for (kj = 0; kj < R; ++kj) { //carry dependency}

for(ki = 0; ki < S; ++ki) { //carry dependency</pre>

9

grad input(img, ifm, ij + kj, ii + ki) +=

10

grad_output(img, ofm, oj, oi) *

11

weight(ifm, ofm, kj, ki);

12

} } } } }

```

Figure 3.1: Pseudo code of naive direct convolution for back propagation

#### 3.1 Naive Direct Convolution for Back Propagation

A pseudo code of naive direct convolution for back propagation is given in Figure 3.1\*. As we can see, it has seven deep loop nests. In the innermost loop, we read data from gradient output tensor and weight tensor. We multiply them and accumulate on gradient input tensor.

We annotate the independent loops as "independent". These loops are easily parallelizable. We also annotate loops carrying some dependency as "carry dependency" and loops across which reduction takes place as "reduction".

## 3.2 Naive Direct Convolution for Weight Update

A pseudo code of naive direct convolution for weight update is given in Figure 3.12. It also has seven deep loop nests like back propagation. But we do slight reordering of the loops to present the computation in a more clean way. In the innermost loop, we read data from gradient output tensor and input tensor. We multiply them and

<sup>\*</sup>array accesses appear within "( )" instead of "[ ]" due to use of macros. A(i, j, k, l) = A [i\*bound of(j)\*bound of(k)\*bound of(l) + j\*bound of(k)\*bound of(l) + l]

```

1 for(ofm = 0; ofm < K; ++ofm) { //independent</pre>

for(ifm = 0; ifm < C; ++ifm) { //independent</pre>

for(img = 0; img < N; ++img) { //reduction</pre>

for (oj = 0; oj < P; ++oj) {//reduction

4

ij = oj * u;

6

for(oi = 0; oi < Q; ++oi) {//reduction}

ii = oi * v;

for (kj = 0; kj < R; ++kj)  { //independent

for (ki = 0; ki < S; ++ki) { //independent}

9

grad weight(ofm, ifm, kj, ki) +=

10

11

input(img, ifm, ij + kj, ii + ki) *

grad_output(img, ofm, oj, oi);

12

13

} } } } }

14

```

Figure 3.2: Pseudo code of naive direct convolution for weight update

accumulate on gradient weight tensor. Furthermore, we also annotate the loops in the same way as we do in case of pseudo code for back propagation in Figure 3.1.

### 3.3 Data Layout

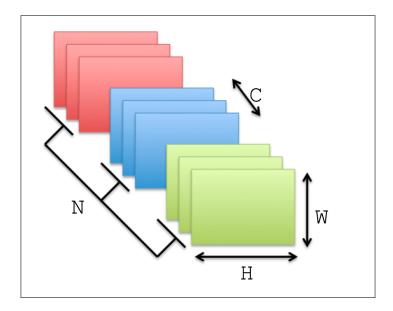

In this section, we consider different layouts of the tensor dimensions. For the reference of what they mean, we give a list of dimensions and their meaning in Table 3.1 and also a pictorial representation of input tensor in Figure 3.3.

The layout of input, output, and weight tensors play a significant role in achieving high throughput for convolution. In general, if the data access pattern matches the data layout, achieving spatial locality becomes much easier, and this is a crucial factor to consider for x86 architectures due to multiple levels of cache and TLB. Existing GPU frameworks such as cuDNN [13] use H and W dimension for vectorization, partly due to efficient scatter/gather support in the GPU architecture. However, from our experience, x86 architectures do not yet support efficient scatter/gather operations. Furthermore, the input feature map, C, and the output feature map, K, are

Table 3.1: Tensor Dimensions

| Dimensions | Description                |

|------------|----------------------------|

| N          | Number of images           |

| С          | Input channel/feature map  |

| K          | Output channel/feature map |

| Н          | Input image height         |

| W          | Input image width          |

| P          | Output image height        |

| Q          | Output image width         |

| R          | Filter/Weight height       |

| S          | Filter/Weight width        |

Figure 3.3: Pictorial representation of input tensor

typically multiples of vector length on IA. So, for vectorization, we block these dimensions by vector length and bring in the blocking factor to the innermost dimension. Now, considering parallelization on back propagation, N and blocked C dimensions are good candidates because the loops corresponding to them are independent as we see in Figure 3.1. Furthermore, they usually have high value, which results in high level of parallelism in the code. So, it makes sense to make N and blocked C the outermost dimensions and parallelize the loops corresponding to these dimensions. Thus our data layout for input tensor becomes to  $I \in NC_{B_I}HWB_I$  format where  $B_I$  denotes the blocking factor of input feature map and is equal to vector length. Similarly, the data layout for output tensor becomes to  $O \in NK_{B_O}PQB_O$  format where  $B_O$  is the blocking factor of output feature map and also equals to vector length. We use same data layouts for input gradient and output gradient tensors.

Now for the weight tensor, which includes dimensions equal to input feature map and also output feature map, we have to decide the blocking factor from which dimension will be the innermost dimension. We use the blocking factor from output feature map for vectorization in both forward pass and weight update, and we only use the blocking factor of input feature map for vectorization in back propagation. So, based on usage frequency, we choose the blocking factor from output feature map as the innermost dimension for weight tensor. Considering parallelism for weight update, blocked C and blocked K are good candidates for parallelism as the loops corresponding to them are independent (Figure 3.12). So, we put them as the outermost dimensions. Thus the data layout for weight tensor becomes to  $W \in K_{Bo}C_{BI}RSB_{I}B_{O}$  format. The weight gradient tensor has similar data layout as weight tensor. We call these data formats collectively as Custom data format and all our optimizations refer to these data formats.

Besides using our Custom data format, we also experimented with the data format

of a state-of-the-art DNN framework that is very popular in the field, namely, Tensorflow [3]. Tensorflow uses *NHWC* format for input and output tensors and *RSCK* format for weight tensor. By comparing performance across different data formats, we gain more insight into the impact of data layout on the performance of direct convolution on KNL.

# 3.4 Optimized Direct Convolution for Back Propagation on KNL

#### 3.4.1 Vectorization

As we talked in section 3.3, our strategy for back propagation is to vectorize along the blocking factor of input feature map. So, we block the *ifm* loop in Figure 3.1 by a factor of vector length on IA and bring that blocking factor loop to the innermost position, i.e. after *ki* loop. Then we vectorize the loop. From the direct convolution loop nests for back propagation shown in Figure 3.1, we can easily see that the computation in the innermost loop follows multiply and accumulate computational pattern. For this computational pattern, we have several fused multiply and add (**fmadd**) vector instructions [14]. For example, **fmadd** operation on 32-bit floating-point data comes with these variants: **vfmadd132ps**, **vfmadd213ps**, **vfmadd231ps**, and **vfmadd233ps**. The first three variants can be represented as follows:

vfmadd132ps::zmm1,zmm2,zmm3 : zmm1 = zmm1xzmm3+zmm2

vfmadd213ps::zmm1,zmm2,zmm3 : zmm1 = zmm2xzmm1+zmm3

vfmadd231ps::zmm1,zmm2,zmm3 : zmm1 = zmm2xzmm3+zmm1

Where **zmm** represents vector registers, "::" represents argument list to a instruction, and ":" represents translation of a instruction to mathematical operation. Memory loads, modifiers such as conversion or broadcast are only applied to **zmm3**. The fourth

**fmadd** variant, i.e. **vfmadd233ps** is a special **fmadd** instruction that acts as scale and bias transformation in one instruction. As we have separate tensors for input, output, and weight, this instruction is not applicable in our case.

Considering the **fmadd** vector instructions, we think **vfmadd231ps** is the most suitable instruction in our case. We implement our multiply and accumulate computation with the following strategy:

- As the data layout of input tensor has  $B_I$  as innermost dimension and it is of vector length, we achieve vectorizing accesses to input. We use **zmm1** for input because we want to accumulate to input.

- Now, the weight tensor has  $B_O$  as the innermost dimension and then  $B_I$ . So, in order to vectorize along  $B_I$  dimension, we transpose weight tensor so that  $B_I$  becomes the innermost dimension. This adds an overhead but if we have to maintain the same data layout for forward pass, back propagation, and weight update, we have pay some penalty in one of the stages because all of the stages do not use same dimension for vectorization. We use **zmm2** for weight.

- The output is then broadcast to a vector register in order to perform vector multiplication. As we need broadcast operation for output and we can use only zmm3 for broadcast, we use zmm3 for output.

So, we perform the multiply and add operation inside our innermost loop in Figure 3.1 with combination of **broadcast** and **fmadd** in a single vector instruction, namely, **vfmadd231ps**. The resulting code after vectorization is shown in Figure 3.4.

#### 3.4.2 Optimize for Temporal and Spatial Locality

Temporal locality and spatial locality are very important factors for achieving peak performance in x86 architectures because of multiple level cache hierarchy and TLB.

```

1 for(img = 0; img < N; ++img) {</pre>

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) { //blocked by VLEN</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for (ofm2 = 0; ofm2 < B_{O}; ++ofm2) {

for(oj = 0; oj < P; ++oj) {

6

ij = oj * u;

for(oi = 0; oi < Q; ++oi) {</pre>

7

ii = oi * v;

8

for (kj = 0; kj < R; ++kj) {

9

for(ki = 0; ki < S; ++ki) {

10

grad_input_vec = vload(gard_input[img][ifm1][ij+kj]

11

[ii+ki][0]);

weight_vec = vload(weight[ofm1][ifm1][kj][ki][ofm2][0]);

12

vfmadd231ps::grad_input_vec, weight_vec,

13

broadcast(grad_output[img][ofm1][oj][oi][ofm2]);

14

vstore(gard_input[img][ifm1][ij+kj][ii+ki][0],

15

grad_input_vec);

16

```

Figure 3.4: Pseudo code for back propagation after vectorization

The code in Figure 3.4 that we get after vectorization can be optimized for temporal locality by blocking for floating-point vector registers (register blocking). If we consider the data layout of input tensor, it becomes apparent that W dimension is ideal candidate for register blocking since it is the innermost dimension after  $B_I$  which is used for vectorization. However, W dimension changes with oi and ki loops. If we block along oi loop, we will achieve temporal locality for weight tensor since it is invariant to oi loop. On the other hand, if we block along ki loop, we will gain temporal locality for output tensor. In case of CNNs, the filter width, S, usually has small value and the output feature width, Q, usually have large enough value. Hence, in order to gain enough temporal locality through register blocking we use oi loop. We unroll-and-jam oi loop and decide the unroll factor based on input parameter values and number of available vector registers. The resulting pseudo code after register blocking is shown in Figure 3.5. The constraint for the unroll factor here is the number of available floating-point vector registers (typically 32 in modern

```

1 for(img = 0; img < N; ++img) {</pre>

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) {</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for (ofm2 = 0; ofm2 < B_{O}; ++ofm2) {

for(oj = 0; oj < P; ++oj) {

ij = oj * u;

6

for(oi = 0; oi < Q/B_Q; ++oi) { //B_Q is equal to

unroll_factor_rb

ii = oi * v;

for (k \dot{\gamma} = 0; k \dot{\gamma} < R; ++k \dot{\gamma}) {

9

for (ki = 0; ki < S; ++ki) {

10

weight_vec = vload(weight[ofm1][ifm1][kj][ki][ofm2][0]);

11

12

grad_input_vec = vload(gard_input[img][ifm1][ij+kj]

13

[oi*B_O*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

14

broadcast (grad_output[img][ofm1][oj][oi\star B_Q][ofm2]);

vstore(gard_input[img][ifm1][ij+kj][oi*B_Q*v+ki][0],

15

grad_input_vec);

16

17

grad_input_vec = vload(gard_input[img][ifm1]

[ij+kj][(oi*B_Q+1)*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

18

broadcast (grad_output[img][ofm1][oj][oi\star B_Q+1][ofm2]);

vstore(gard_input[img][ifm1]

19

[ij+kj][(oi*B_Q+1)*v+ki][0],grad_input_vec);

20

\dots //B_Q times

```

Figure 3.5: Pseudo code for back propagation after 1-D register blocking

x86 architectures). However, we set aside at least 4 floating-point vector registers for other purposes (described later). Then the number of floating-point vector registers available for register blocking becomes 28. So, we set the unroll factor as follows:  $unroll_factor_rb = min(Q, divider of Q lower than 28)$  where rb denotes register blocking. Typically the value of Q is high enough that 1-D register blocking suffices. If the value of Q is so small that 1-D register blocking does not suffice, we go for 2-D register blocking which includes another level of register blocking along oj loop.

The code from Figure 3.5 can be further optimized to gain spatial locality and more temporal locality by blocking for L1 data cache (cache blocking). Since we are broadcasting one element of output tensor at each **fmadd** instruction and the innermost dimension of output tensor is  $B_O$ , we can gain spatial locality in output tensor access by bringing ofm2 loop inside ki loop. Here, we make the assumption that unroll\_factor\_rb \*  $B_O$  output element fits in the L1 cache. In our case, unroll\_factor\_rb  $\leq$  28 and  $B_O$  is VLEN which is typically a cache line size on IA for AVX-512. Since we are considering 28 cache lines and L1 cache can contain up to 512 cache lines, our assumption is quite reasonable. Besides bringing spatial locality, this L1 cache blocking along ofm2 loop also brings temporal locality in input tensor access because accumulation occurs on the same input values along ofm2 loop. The resulting code after L1 cache blocking is given in Figure 3.6.

#### 3.4.3 Optimize loads and stores

We do vector load operation on weight and input tensor and vector store operation on input tensor. We do not perform vector load on output tensor, but we perform broadcast instead, i.e. one element of output tensor is broadcast to all the lanes of vector register containing values from weight tensor. The code from Figure 6 can be further optimized regarding loads and stores. First, we consider the vector loads of weight tensor. The **fmadd** instructions are dependent on the weight vector load that precedes them. Therefore a cache miss on weight load can cause havoc on performance because it will stall all the **fmadd** instructions following it. In order to eliminate such stalls, we schedule the weight vector loads in advance at the cost of a moderate increase in register pressure. We use 4 floating-point vector registers for loading weights in advance and setting up a 4-register ring-buffer of vector loads on weight tensor.

```

1 for(img = 0; img < N; ++img) {</pre>

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) {</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for(oj = 0; oj < P; ++oj) {

ij = oj * u;

for (oi = 0; oi < Q/B_Q; ++oi) { //B_Q is equal to

6

unroll_factor_rb

ii = oi * v;

for (kj = 0; kj < R; ++kj) {

for (ki = 0; ki < S; ++ki) {

9

10

{ weight_vec = vload(weight[ofm1][ifm1][kj][ki][0][0]);

11

grad_input_vec = vload(gard_input[img][ifm1][ij+kj]

12

[oi*B_O*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

broadcast (grad_output[img][ofm1][oj][oi*B_Q][0]);

vstore (gard_input[img][ifm1][ij+kj][oi*B_Q*v+ki][0],

14

grad_input_vec);

15

grad_input_vec = vload(gard_input[img][ifm1]

16

[ij+kj][(oi*B_Q+1)*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

17

broadcast (grad_output[img][ofm1][oj][oi*B_Q+1][0]);

vstore(gard_input[img][ifm1]

18

[ij+kj] [(oi*B_Q+1)*v+ki][0],grad_input_vec);

19

\dots //B_Q times

20

21

22

{ weight_vec = vload(weight[ofm1][ifm1][kj][ki][1][0]);

23

24

grad_input_vec = vload(gard_input[img][ifm1][ij+kj]

[oi*B_Q*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

26

broadcast (grad_output[img][ofm1][oj][oi\star B_Q][1]);

vstore (gard_input[img][ifm1][ij+kj][oi*B_Q*v+ki][0],

grad_input_vec);

28

grad_input_vec = vload(gard_input[img][ifm1]

29

[ij+kj][(oi*B_Q+1)*v+ki][0]);

vfmadd231ps::grad_input_vec, weight_vec,

30

broadcast (grad_output[img][ofm1][oj][oi\star B_Q+1][1]);

vstore(gard_input[img][ifm1]

31

[ij+kj] [(oi*B_Q+1)*v+ki][0],grad_input_vec);

32

\dots //B_Q times

33

35

\dots //B_O times

37 } } } } }

```

Figure 3.6: Pseudo code for back propagation after L1 cache blocking

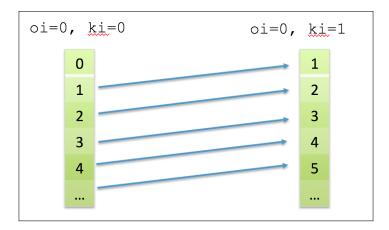

Figure 3.7: Access pattern for input when stride is 1

The scenario for vector load and store on input tensor is little tricky. From Figure 3.6, we see that we need unroll\_factor\_rb number of vector length inputs in each iteration of ki. However, after carefully analyzing input access pattern along W dimension, we see that, as ki varies from one iteration to another iteration, there is a significant reuse in input access if the stride along W dimension is one. The scenario is depicted in Figure 3.7. In case of CNNs, the stride is one most of the times. Hence, if we take advantage of the reuse of input data, we can reduce the number of vector loads and stores significantly on input data. The strategy we use is as follows:

- In the first iteration of *ki*, we load all the unroll\_factor\_rb vector length inputs. Lets index them by 0 to (unroll\_factor\_rb-1)

- Then for the next iteration, we need vector length inputs from 1 to unroll\_factor\_rb.

So, from next iteration of ki, we load only one vector length input that has

the next index to the last index from the previous iteration.

- We shift and rotate the register indices so that **fmadds** are performed on corresponding right floating-point vector registers.

- We store the vector register that has the first index for the current iteration. If

it is the last iteration of ki, we store all the vector registers.

We unroll ki loop completely and employ the load/store strategy mentioned above. Moreover, it also reduces branching in the code. Although the value of R and S are usually small, typically we unroll only ki loop. This is because the code needs to fit in the L1 instruction cache. We discuss this in detail in section 3.4.5. After optimizing the vector loads and stores, the pseudo code becomes the one given in Figure 3.8.

#### 3.4.4 Runtime Code Specialization and Parallelization

As we discussed at the beginning of chapter 3, we cannot achieve peak performance through static compilation in case of direct convolution on CNNs because of widely varying values of input parameters. Our optimization strategy and factors depend on these input parameter values, and these dynamic values are only known at execution time. So, our approach is to perform runtime code specialization, and we do so with the help of SMALLGEMM jus-in-time assembly generator [12].

The innermost code sequence starting from kj loop in Figure 3.8 is abstracted out to the SMALLGEMM JITer. The assembly code for this code sequence is generated before entering the loop nest as shown in Figure 3.9. The  $bp\_jit$  function pointer takes the convolution parameters as a descriptor and generates an optimal sequence of x86 instructions. Since we generate the JITed code only at the setup phase and the cost of code generation by SMALLGEMM is very low, there is virtually no overhead of JITing in our case. Furthermore, we can generate more than one version of specialized JITed code and use the appropriate version in the corresponding scenario. However, there are two constraints when aiming for peak performance with this approach. We have to ensure that the code fits in L1 instruction cache while switching between multiple versions of the JITed code and the memory footprint of each JITed code fits in the L1 data cache. Fortunately, it is easy to do so in our case. As we keep the loop

```

1 for(img = 0; img < N; ++img) {</pre>

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) {</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for(oj = 0; oj < P; ++oj) {</pre>

ij = oj * u;

for (oi = 0; oi < Q/B_Q; ++oi) {

6

ii = oi * v;

for (kj = 0; kj < R; ++kj) {

for(ki = 0; ki < S; ++ki) { //unrolled, but represented</pre>

//here as loop to give cleaner logical view of the code

weight_vec_0 = vload(weight[ofm1][ifm1][kj][ki][0][0]);

weight_vec_1 = vload(weight[ofm1][ifm1][kj][ki][1][0]);

11

weight_vec_2 = vload(weight[ofm1][ifm1][kj][ki][2][0]);

weight_vec_3 = vload(weight[ofm1][ifm1][kj][ki][3][0]);

13

14

if (ki == 0) {

15

vload B_Q VLEN grad_inputs starting from

16

grad_input[img][ifm1][ij+kj][oi*B_Q*v][0];

17

} else {

vload (grad_input[img][ifm1][ij+kj][(oi*B_Q+(B_Q+ki-1))*v

[0];

19

}

20

{ //starting index for grad_input_vec_reg is determined by

//rotating register indices

22

vfmadd231ps::grad_input_vec_reg_start, weight_vec_0,

broadcast (grad_output[img][ofm1][oj][oi*B_Q][0]);

vfmadd231ps::grad_input_vec_reg_start+1, weight_vec_0,

broadcast(grad_output[img][ofm1][oj][oi\star B_Q+1][0]);

25

...}

26

27

weight_vec_4 = vload(weight[ofm1][ifm1][kj][ki][4][0]);

28

29

vfmadd231ps::grad_input_vec_reg_start, weight_vec_1,

broadcast (grad_output[img][ofm1][oj][oi*B_Q][1]);

vfmadd231ps::grad_input_vec_reg_start+1, weight_vec_1,

broadcast (grad_output [img] [ofm1] [oj] [oi\star B_Q+1] [1]);

. . .

33

if (ki == (S-1)) {

vstore B_Q grad_input_regs;

35

} else {

vstore grad_input_vec_reg_start;

37

} } } } }

39

```

Figure 3.8: Pseudo code for back propagation after optimization of loads and stores

```

1 bp_desc = setup backward descriptor using N,C,H,W,K,R,S,u,v,pad_h,

2 conv_bp = bp_jit(bp_desc, ...); //Call to JITer to generate JIT

code at Runtime

3 #pragma omp for collapse(2)

4 \text{ for (img = 0; img < N; ++img) }

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) {</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for(oj = 0; oj < P; ++oj) {

ij = oj * u;

for (oi = 0; oi < Q/B_Q; ++oi) {

float *inp_ptr = &(grad_input[img][ifm1][ij][oi*B_Q*v][0]);

10

const float *out_ptr = &(grad_output[img][ofm1][oj]

[oi*B_O][0];

const float *wt_ptr = &(weight[ofm1][ifm1][0][0][0][0]);

conv_bp(input_ptr, wt_ptr, out_ptr);

14 } } } }

```

Figure 3.9 : Pseudo code for back propagation after runtime code specialization and parallelization

nests for register and cache blocking outside of our JITer, we can control the code size and memory footprint fairly easily. The memory footprint of  $bp\_jit$  in bytes can be computed as follows:

$$Mem(\texttt{bp-jit}) = B_Q * B_O * 4 (for \ output) +$$

$$R * S * B_O * VLEN * 4 (for \ weight) +$$

$$R * (B_O + S) * VLEN * 4 (for \ input)$$

(3.1)

The parameters  $B_O$ ,  $B_Q$ , unroll factor of ki loop, and unroll factor of kj loop are chosen such that  $Mem(p_jit)$  is less than L1 data cache size (typically 32 KB in Intel x86 Architectures). Moreover, we also ensure that the code size of  $p_jit$  and all of its variants generated at runtime is less than L1 instruction cache size (typically 32 KB in IA). We discuss this in detail in section 3.4.5.

As we can see in Figure 3.9, we dedicate our JITer to generate highly optimized code

only for the most critical innermost loop nests. We still leverage a regular compiler for parallelizing and optimizing outer loop nests. Having the outer loop nests in high-level language has several advantages. They can be easily parallelized using widely available threading libraries, such as OpenMP. In our case, the outermost img loop and blocked ifm1 loop are independent and easily parallelizable. Furthermore, the minibatch size, N, usually have high value. So, the minibatch loop together with ifm1 loop exhibits sufficient thread-level parallelism for x86 architectures. Hence, we use them to exploit thread-level parallelism via OpenMP constructs such as **collapse** and **pragma omp parallel**.

#### 3.4.5 Optimize Code Size

In order to achieve peak performance on x86 architecture, we have to ensure that the code fits in L1 instruction cache. Otherwise, we have to pay a huge penalty for fetching it from lower level caches or main memory. The parameters that affect JITed code size is  $B_O$ ,  $B_Q$ , unroll factor of ki loop, and unroll factor of kj loop. Now for determining code size, we take a nave approach. We use a simple heuristic where we have an empirical value of the code size when all these parameters have a value of 1. Now we multiply that code size with the values of these parameters and get a projection of the final JITed code size. Depending on the values of code size, we determine whether to unroll ki loop and or kj loop. On KNL, we typically unroll only ki loop.

Besides these parameters, there is also another issue that can increase the code size and negatively affect the performance. As Xeon Phi does not have a decoded instruction cache, AVX-512 code quality plays an important role in achieving good performance. A general rule that we have to follow in this case is that only up to 16 Bytes can be fetched per cycle from the instruction cache. This constraint becomes

problematic in the case of our **fmadd** operations. When reading output in a broadcast fashion, we have strided access by a factor of  $B_O$ . This sometimes results in an offset larger than 1024 bytes between broadcasts. In such a case, the length of the **fmadd** instruction increases from 7 to 10 bytes and instructions with this increased length cannot be fetched on a sustainable basis from the instruction cache. So, we utilize x86 SIB (scale index base) addressing mode to reduce the instruction size to 8 bytes per **fmadd** operation. Since we have spare general purpose (gp) registers, we use them for expressing up to 28 streams. The strategy is as follows:

- In SIB mode an address is represented as  $(Base\ Address + Scale * Index)$

- We load the size of  $B_O$  in a gp register. We also store  $3*B_O$ ,  $5*B_O$ , and  $7*B_O$  in three other gp registers. We use these registers as index registers.

- Due to scaling in SIB mode,  $\{1,2,4,8\}$  \* any index register value can be added for free. Hence, we are now able to express 9 addresses with stride  $B_O$  starting from a *Base Address*.

- Further storing  $BaseAddress + \{9, 18, 27\} * B_O$  in three different gp registers, we are now able to express up to 28 addresses with the stride of  $B_O$ .

#### 3.4.6 Hiding fmadd Latency

As discussed in section 2.2, each KNL core has two VPUs. The latency of each VPU is 6 cycles. So, if our vector floating-point register blocking is less than 12, we issue a **fmadd** instruction to a VPU before it has finished executing the previous **fmadd** instruction on a vector register. This creates **fmadd** stalls and bubble in the pipeline. To avoid this kind of situation, we proposed in section 3.4.2 a 2-D register blocking, i.e. another level of register blocking along H dimension. However, we cannot make register blocking arbitrarily large. We have the upper limit set to 28 vector floating-

pointer registers for this purpose. Sometimes the values of H and W may prevent us doing 2-D register blocking within this constraint. For example, the scenario where H = 7 and W = 7. In this kind of scenario, we use another strategy to hide **fmadd** latency. We use extra accumulator registers and store partial results alternatively in those accumulators. At the end of the convolution, we sum up the result to get the final value of a register. This strategy transforms dependent instructions to independent instructions as we have decoupled the destination registers.

#### 3.4.7 Software Prefetch

Intel x86 ISA has explicit L1 and L2 cache prefetch instructions in the form of **prefetcht0** and **prefetcht2**, respectively. We use these instructions in our JITer to prefetch the required data from one JITed function call to another. We extended the JITer interface with additional arguments that hold the address for input, output, and weight tensor accesses for the next JITed function call. As we discussed in section 3.4.3, we schedule weight loads in advance. So, our prefetch strategy is to prefetch the weights to L2 cache, but prefetch input and output to L1 cache. The input prefetches are inserted along the input vector loads and that makes total  $R*(B_O+S)$  input prefetches, which amounts to  $R*(B_O+S)*64$  bytes of input data being brought to L1 data cache. This is because a single prefetch instruction brings one cache line size of data and cache line size in IA is typically 64 bytes. We insert the output prefetches along **fmadd** instructions until all the required  $B_Q$  cache lines are prefetched. This results in  $B_Q*64$  bytes of output data being brought to L1 data cache. We also insert the weight prefetches along **fmadd** instructions, which results in  $R*S*B_O*64$  bytes of weight data being prefethed to L2 cache.

We can see from Figure 3.9, the weight tensor is reused across oi and oj loop. Since weights are reused, there is no need to prefetch weight inside oi and oj loop.

```

1 bp_desc = setup backward descriptor using N,C,H,W,K,R,S,u,v,pad_h,

2 conv_bp_pf_noweight = bp_jit(bp_desc, PREFETCH_NO_WEIGHT); //JITed

code without weight prefecth

3 conv_bp_pf = bp_jit(bp_desc, PREFETCH_ALL); //JITed code with

weight prefecth

4 #pragma omp for collapse(2)

5 \text{ for (img = 0; img < N; ++img) }

for(ifm1 = 0; ifm1 < C/VLEN; ++ifm1) {</pre>

for (ofm1 = 0; ofm1 < K/B_O; ++ofm1) {

for(oj = 0; oj < P; ++oj) {

9

ij = oj * u;

for (oi = 0; oi < Q/B_Q; ++oi) {

10

float *inp_ptr = &(grad_input[img][ifm1][ij][oi*B_O*v][0]);

11

const float *out_ptr = &(grad_output[img][ofm1][oj]

[oi * B_Q][0]);

const float *wt_ptr = &(weight[ofm1][ifm1][0][0][0][0]);

13

if ( not last iteration of oj loop) {

14

//do not prefetch weights

15

conv_bp_pf_noweight(input_ptr, wt_ptr, out_ptr,

16

17

& (grad_input[img][ifm1][ij][(oi+1)*B_O*v][0]),

NULL, //weights are not prefetched

18

& (grad_output[img][ofm1][oj][(oi+1) \star B_Q][0]);

19

20

} else { //last iteration of oj loop, prefetch weights

21

conv_bp_pf(input_ptr, wt_ptr, out_ptr,

22

23

& (grad_input[img][ifm1][0][0][0]),

& (weight [ofm1+1] [ifm1] [0] [0])

24

& (grad_output[img][ofm1+1][0][0]);

25

27 } } } }

```

Figure 3.10: Pseudo code for back propagation with JIT interface and software prefetching

We only need to prefetch weight at the end of oj loop. So, to prevent redundant weight prefetch, we generate two versions of JITed code, one without weight prefetch (conv\_bp\_pf\_noweight) and another with weight prefetch (conv\_bp\_pf). The resulting code with software prefetching is shown in Figure 3.10.

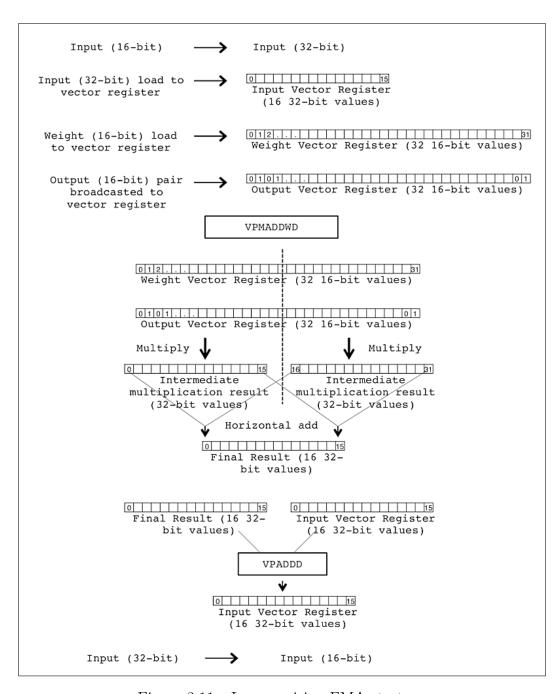

#### 3.4.8 Low Precision Operations

In general, the data associated with CNNs are represented in 32-bit single precision floating points. But, currently, there is a growing interest within the community to present the data associated with CNNs in low precision format and perform convolution on these low precision data to accelerate the computation. We also investigated on this topic of performing convolution efficiently for low precision data, on Intel x86 architecture. Intel Software Developers Manual March 2017 update [15] includes some instructions that are of interest considering our objective here.

First, let us consider the low precision formats and configurations that we can have 1) 16-bit data and 32-bit accumulator, 2) 8-bit data and 16-bit accumulator, 3) 8-bit data and 32-bit accumulator. The general optimization strategies that we talked earlier remain more or less same for convolution in these low precision formats, except the strategy to perform fused multiply-adds (FMA) inside the innermost loop. So, we present our revised strategy to perform FMA in these low precision formats here. 1) 16-bit data and 32-bit accumulator. In general for low precision computation, we reserve one floating point vector register storing pairs of output data, and one other for storing the result of partial sum. As a result, we have 26 vector registers for register blocking instead of 28 vector registers.

- We convert input data from 16-bit to 32-bit before passing the input tensor pointer to the JITed function.

- During weight loads, we load 32 16-bit weight elements into a vector register.

- For performing FMA, we first broadcast a pair of 16-bit values from output tensor to one of our reserved vector register using **VPBROADCASTD** instruction.

- Then we perform 16-bit multiply and add with horizontal add using **VPMADDWD** instruction. It multiplies the individual signed words of the destination operand

with the corresponding signed words of the source operand, producing temporary signed doubleword results. The adjacent doubleword results are then summed (we refer to this as horizontal add) and stored in the destination operand, the other reserved vector register used for storing partial sums.

- We then add this result to vector register containing input tensor values. We use **VPADDD** instruction for this.

- After returning from of the JITed function call, we convert input data from 32-bit to 16-bit.

The whole process is depicted in Figure 3.11.

- 2) 8-bit data and 16-bit accumulator the strategy is exactly same as the one described for 16-bit data and 32-bit accumulator. The only exceptions are We use **VPBROADCASTW** instruction for broadcasting pairs of 8-bit output values, **VPMADDUBSW** instruction for doing FMA with horizontal add, and **VPADDW** instruction for adding the intermediate result to input vector register.

- 3) 8-bit data and 32-bit accumulator the strategy, in this case, is similar to what we stated for 16-bit data and 32-bit accumulator scenario. However, we need one more vector register to perform horizontal add between intermediate 16-bit results. So, now we are left with 25 vector registers for register blocking.

- We convert input data from 8-bit to 32-bit before calling the JITed function.

- During weight loads, we load 64 8-bit weight tensor values into a vector register.

- We broadcast quadruple of 8-bit output tensor values to a vector register.

- Then we perform 8-bit FMA with horizontal add using **VPMADDUBSW** instruction which produces 16-bit intermediate results.

- We further perform horizontal add of these results. For this, we preload one vector register with 32 16-bit 1s. We use this vector register to perform FMA with horizontal add on 16-bit intermediate values which results in 32-bit horizontal add because one operand of the multiplications is 1. We use **VPMADDWD** instruction for this purpose.

- Then we add these 32-bit partial sums to input register using **VPADDD** instruction.

- After returning from JITed function, we convert back input data from 32-bit to 8-bit.

#### 3.4.9 Packed fmadd Operations

Another interesting class of instructions from Intel x86 ISA [16] that is relevant to our case is packed single-precision floating-point **fmadd** instructions. We are specifically interested in **V4FMADDPS** instruction. This instruction computes four sequential packed fused multiply add instructions with a sequentially selected memory operand in each of the four steps. The instruction works as follows:

**V4FMADDPS**:: **zmm1**, **zmm2+3**, **m128**- it accesses four source registers starting with **zmm2**; sources are consecutive and start in a multiple-of-4 boundary. It multiplies packed single-precision floating-point values from these source registers by values from **m128** and accumulates the result in **zmm1**.

We use this instruction to execute efficiently four **fmadd**s together in a single instruction if the blocking factor  $B_O$  (Figure 3.10) of output feature map is divisible by 4, which is typically the case. We replace each sequence of 4 **vfmadd231ps** instructions along BO with one **v4fmaddps**. One downside of this approach, we cannot set up a 4-register ring-buffer for weight loads as described in section 3.4.3 because now we need four source registers for weight data in each step.

Figure 3.11: Low precision FMA strategy

```

1 for(ofm = 0; ofm < K; ++ofm) { //independent</pre>

for(ifm = 0; ifm < C; ++ifm) { //independent</pre>

for(img = 0; img < N; ++img) { //reduction</pre>

for (oj = 0; oj < P; ++oj) {//reduction

ij = oj * u;

for (oi = 0; oi < Q; ++oi) {//reduction}

ii = oi * v;

for (kj = 0; kj < R; ++kj)  { //independent

for (ki = 0; ki < S; ++ki) { //independent}

9

grad weight(ofm, ifm, kj, ki) +=

10

input(img, ifm, ij + kj, ii + ki) *

11

12

grad_output(img, ofm, oj, oi);

13

14 } } } } }

```

Figure 3.12: Pseudo code of naive direct convolution for weight update

## 3.5 Optimized Direct Convolution for Weight Update on KNL

For convenience of understanding, we reproduce Figure 3.12 here.

The optimizations that we applied to direct convolution in back propagation also applies here. So, we will only talk about the details that are different for weight update from back propagation.

#### 3.5.1 Vectorization

For direct convolution in weight update, we vectorize along the blocking factor  $B_O$  of output feature map because weight tensor and output tensor both have  $B_O$  as their innermost dimension. So, we block the ofm loop by vector length VLEN and bring that loop to the innermost position and then vectorize. We do the fused multiply add operation using **vfmadd231ps** instruction as we did in section 3.4.1 with change in vector register arguments. As we are accumulating to weight tensor now, we use **zmm1** for weight tensor. We broadcast input tensor value to **zmm3** and use **zmm2** for output tensor. The resulting code is shown in Figure 3.13.

```

1 for(ofm1 = 0; ofm1 < K/VLEN; ++ofm1) { //blocked by VLEN</pre>

for (ifm1 = 0; ifm1 < C/B_I; ++ifm1) {

for (ifm2 = 0; ifm2 < B_I; ++ifm2) {

for (img = 0; img < N; ++img)

for(oj = 0; oj < P; ++oj) {

6

ij = oj * u;

for(oi = 0; oi < Q; ++oi) {</pre>

ii = oi * v;

for (kj = 0; kj < R; ++kj) {

9

for(ki = 0; ki < S; ++ki)

10

grad_weight_vec = vload(gard_weight[ofm1][ifm1][kj][ki][

11

ifm2][0]);

output_vec = vload(output[img][ofm1][oj][oi][0]);

12

vfmadd231ps:: grad_weight_vec, grad_output_vec,

13

broadcast(input[img][ifm1][ij+kj][ii+ki][ifm2]);

vstore(gard_weight[ofm1][ifm1][kj][ki][ifm2][0],

15

grad_weight_vec);

16

```

Figure 3.13: Pseudo code for weight update after vectorization

#### 3.5.2 Optimize for Temporal and Spatial Locality

We do a 2-D cache blocking along oi and oj loops in order to get temporal locality along weight tensor accesses. We register block on ifm loop and gain spatial locality for input tensor accesses and temporal locality for output tensor accesses. The pseudo code for weight update, after performing register blocking and cache blocking, is given in Figure 3.14.

### 3.5.3 Optimize loads and stores

To optimize load and stores of weight tensor, we hoist weight tensor loading and storing outside  $oj\_b$  loop because it does not depend on output feature height, P, and output feature width, Q. We set up a 4-register ring buffer for output loads to load outputs in advance to their use in corresponding **fmadd**s; similar to what we do for weight loads in section 3.4.3. The resulting code is given in Figure 3.15.

```

1 for(ofm1 = 0; ofm1 < K/VLEN; ++ofm1) { //blocked by VLEN</pre>

for (ifm1 = 0; ifm1 < C/B_I; ++ifm1) {

for(img = 0; img < N; ++img) {</pre>

for (oj = 0; oj < P/B_P; ++oj) {

ij = oj * u;

5

for (oi = 0; oi < Q/B_Q; ++oi) {

ii = oi * v;

for (kj = 0; kj < R; ++kj) {

for(ki = 0; ki < S; ++ki) {</pre>

10

for (oj_b = 0; oj_b < B_P; ++oj_b)  { //unrolled

for (oi_b = 0; oi_b < B_Q; ++oi_b) { //unrolled

11

grad_weight_vec = vload(gard_weight[ofm1][ifm1][kj][ki

12

][0][0]);

output\_vec = vload(output[img][ofm1][oj*B_P+oj\_b][oi*

13

B_{Q}+\text{oi\_b}][0]);

vfmadd231ps:: grad_weight_vec, grad_output_vec,

14

broadcast (input [img] [ifm1] [ (oj*B_P+oj_b) *u+kj] [ (oi*

B_Q+oi_b) *v+ki][0]);

vstore(gard_weight[ofm1][ifm1][kj][ki][0][0],

15

grad_weight_vec);

16

grad_weight_vec = vload(gard_weight[ofm1][ifm1][kj][ki

17

][1][0]);

output_vec = vload(output[img][ofm1][oj*B_P+oj_b][oi*

18

B_{Q}+\text{oi\_b}][0]);

vfmadd231ps:: grad_weight_vec, grad_output_vec,

19

broadcast (input [img] [ifm1] [ (oj*B_P+oj_b) *u+kj] [ (oi*

B_O+oi_b) *v+ki][1]);

vstore(gard_weight[ofm1][ifm1][kj][ki][1][0],

20

grad_weight_vec);

21

```

Figure 3.14 : Pseudo code for weight update after 2-D register blocking and cache blocking

```

1 for(ofm1 = 0; ofm1 < K/VLEN; ++ofm1) { //blocked by VLEN</pre>

for (ifm1 = 0; ifm1 < C/B_I; ++ifm1) {

for(img = 0; img < N; ++img) {</pre>

for (oj = 0; oj < P/B_P; ++oj) {

ij = oj * u;

for (oi = 0; oi < Q/B_Q; ++oi) {

6

ii = oi * v;

for (kj = 0; kj < R; ++kj) {

8

for (ki = 0; ki < S; ++ki) {

9

grad_weight_vec_0 = vload(gard_weight[ofm1][ifm1][kj][ki

10

][0][0]);

grad_weight_vec_1 = vload(gard_weight[ofm1][ifm1][kj][ki

11

][1][0]);

12

for (oj_b = 0; oj_b < B_P; ++oj_b)  { //unrolled

output_vec_0 = vload(output[img][ofm1][oj*B_P+oj_b][oi*

14

B_Q ] [0]);

output_vec_1 = vload(output[img][ofm1][oj*B_P+oj_b][oi*

15

B_Q+1][0]);

output_vec_2 = vload(output[img][ofm1][oj*B_P+oj_b][oi*

16

B_{O}+2][0]);

output_vec_3 = vload(output[img][ofm1][oj*B_P+oj_b][oi*

17

B_Q+3][0]);

18

vfmadd231ps:: grad_weight_vec_0, grad_output_vec_0,

19

broadcast (input [img] [ifm1] [ (oj*B_P+oj_b) *u+kj] [ (oi*

B_O) *v+ki][0]);

vfmadd231ps:: grad_weight_vec_1, grad_output_vec_0,

20

broadcast(input[img][ifm1][(oj*B_P+oj\_b)*u+kj][(oi*

B_O) *v+ki][1]);

21

output_vec_4 = vload(output[img][ofm1][oj*B_P+oj_b][oi*

23

B_Q+4 [0]);

vfmadd231ps:: grad_weight_vec_0, grad_output_vec_1,

24

broadcast (input [img] [ifm1] [ (oj*B_P+oj_b) *u+kj] [ (oi*

B_{O}+1) *v+ki][0]);

vfmadd231ps:: grad_weight_vec_1, grad_output_vec_1,

25

broadcast (input [img] [ifm1] [ (oj*B_P+oj_b) *u+kj] [ (oi*

B_Q+1) *v+ki][1]);

26

27

vstore(gard_weight[ofm1][ifm1][kj][ki][0][0],

29

grad_weight_vec_0);

vstore(gard_weight[ofm1][ifm1][kj][ki][1][0],

30

grad_weight_vec_1);

31

32 } } } } }

```

Figure 3.15: Pseudo code for weight update after optimizing loads and stores

#### 3.5.4 Runtime Code Specialization and Parallelization

As discussed in section 3.4.4, we use SMALLGEMM jus-in-time assembly generator [12] for runtime code specialization. In case of weight update, we take the code sequence inside ki loop in Figure 3.15 and abstract it out using SMALLGEMM JITer.

In Figure 3.15, the independent loops, which are easily parallelizable, are ofm1, ifm1, kj, and ki. Among these loops, kj and ki loops carry significant reuse for input tensor. So, we only parallelize ofm1 and ifm1 loops for thread-level parallelism on x86 architecture. However, sometimes this results in limited parallelism for some layers of popular CNNs. One solution is to try to parallelize img loop. But this loop is a reduction loop in weight update. So, we use thread local weight tensor buffer in this special case, for storing partial results. Then we do parallel reduction over these thread-local buffers to get the final results. Here, we pay a moderate cost in terms of memory requirement to gain more parallelism. The pseudo code with JIT interface and thread-level parallelism is given in Figure 3.16.

### 3.5.5 Software Prefetch

As discussed in section 3.4.7, we do software prefetch in JITed function to prefetch the data required for next JITed function invocation. In case of weight update, we need to prefetch in general  $B_P*B_Q*B_I$  input elements,  $B_P*B_Q*VLEN$  output elements, and  $B_I*VLEN$  weight elements in a JITed function call. However, there are some corner cases. For example, we reuse the output elements across ki and kj loops. We do not need to prefetch output data for JITed function calls within these loops. Hence, we generate two variants of JITed code for weight update, one with output prefetch  $(conv\_wt\_pf)$  and another with no output prefetch  $(conv\_wt\_pf\_nooutput)$ . The pseudo code for weight update with software prefetching is given in Figure 3.17.

```

1 wt_desc = setup weight update descriptor using N,C,H,W,K,R,S,u,v,

pad_h,pad_w;

2 conv_wt = wt_jit(wt_desc, ...); //Generate JIT code

3 if (enough parallelism) {

temp_wt_ptr = &(weight[0][0][0][0][0]);

5 #pragma omp for collapse(2)

6 } else { //not enough parallelism

temp_wt_ptr = &(thread_local_wt_tensor);

8 #pragma omp for collapse(3)

10 for(ofm1 = 0; ofm1 < K/VLEN; ++ofm1) {</pre>

for (ifm1 = 0; ifm1 < C/B_I; ++ifm1) {

for (img = 0; img < N; ++img) {

for (oj = 0; oj < P/B_P; ++oj) {

13

for (oi = 0; oi < Q/B_Q; ++oi) {

14

for (kj = 0; kj < R; ++kj) {

for(ki = 0; ki < S; ++ki) {

16

const float *inp_ptr = &(grad_input[img][ifm1][oj*B_P*u+kj

][oi*B_Q*v+ki][0]);

const float *out_ptr = & (grad_output[img][ofm1][oj*B_P][oi*

B_Q ] [0]);

float *wt_ptr = &(temp_wt_ptr[ofm1][ifm1][kj][ki][0][0]);

conv_wt(input_ptr, wt_ptr, out_ptr);

20

21 } } } } }

```

Figure 3.16 : Pseudo code for weight update after runtime code specialization and parallelization

```

1 wt_desc = setup weight update descriptor using N,C,H,W,K,R,S,u,v,

pad_h,pad_w;

2 conv_wt_pf = wt_jit(wt_desc, PREFETCH_ALL);

3 conv_wt_pf_nooutput = wt_jit(wt_desc, PREFETCH_NO_OUTPUT);

4 if (enough parallelism) {

temp_wt_ptr = &(weight[0][0][0][0][0]);

6 #pragma omp for collapse(2)

7 } else { //not enough parallelism

temp_wt_ptr = &(thread_local_wt_tensor);

9 #pragma omp for collapse(3)

10 }

in for(ofm1 = 0; ofm1 < K/VLEN; ++ofm1) {

for(ifm1 = 0; ifm1 < C/BI; ++ifm1) {</pre>

for(img = 0; img < N; ++img) {</pre>

13

for(oj = 0; oj < P/BP; ++oj) {

14

for(oi = 0; oi < Q/BQ; ++oi) {</pre>

15

16

for (kj = 0; kj < R; ++kj) {

for(ki = 0; ki < R; ++ki) {</pre>

17

const float *inp_ptr = &(grad_input[img][ifm1][oj*BP*u+kj]

[oi*BQ*v+ki

19

][0]);

const float *out_ptr = &(grad_output[img][ofm1][oj*BP][oi*

20

BQ][0]);

float *wt_ptr = &(temp_wt_ptr[ofm1][ifm1][kj][ki][0][0]);

21

if (within kj loop) {

conv_wt_pf_nooutput(input_ptr, wt_ptr, out_ptr,

23

input_prefetch_ptr,

24

weight_prefetch_ptr,

25

NULL //No output prefetch);

26

} else {

27

conv_wt_pf(input_ptr, wt_ptr, out_ptr,

28

input_prefetch_ptr,

29

weight_prefetch_ptr,

30

output_prefetch_ptr);

31

}

32

33 } } } } }

```

Figure 3.17: Pseudo code for weight update with software prefetching

# Chapter 4

## Performance Results on KNL

We evaluated our optimized implementation of direct convolution for back propagation and weight update on Intel x86 platform named Knights Landing (KNL). We give our performance results on a single-socket Intel Xeon Phi 7250 processor with 68 cores, 1.2 GHz mesh-clock, 16 GB MCDRAM@7.2 GT, 96 GB DDR4-2400, FLAT memory mode and QUADRANT cluster mode. For details, one can look into [10]. In our experiments, we enabled Turbo mode, which makes the processor run at 1.3 GHz. We use the Intel®C++ Compiler (ICC) with "-02" flag for the compilation. All the data were kept in the MCDRAM instead of DDR4 for higher bandwidth and latency. We achieve this by using "numact1 membind=1". We use 64 threads for all the experiments.

For evaluation of performance across different state-of-the-art CNNs, we choose five popular CNNs - Alexnet [5], Overfeat [17], Vgga [18], GoogleNet\_V1 [19], and Deep-Bench [20]. We select these topologies as each of them will stress several code generation aspects. The most important aspects are: a) the feature map dimensions of Overfeat and Alexnet are close or at the boundary of hardware latencies for FMA units b) odd number for the dimensions of images in Alexnet c) inner layers of Overfeat and Vgga are wide layers which exceed the L1 cache size, therefore cache data management and prefetching properly is a necessity for these cases d) Vgga layers have large feature map dimensions that require sufficient tiling even within the feature maps e) GoogleNet\_V1 has a widely varying configurations from small feature map dimensions to large feature map dimensions, small feature height and width to

Table 4.1: Parameters for Convolutional Layers of AlexNet, Overfeat, and Vgga

| Layers         | W   | Н   | N   | С    | K    | R  | S  | Р   | Q   | Stride |

|----------------|-----|-----|-----|------|------|----|----|-----|-----|--------|

| Alexnet_CONV1  | 227 | 227 | 256 | 3    | 64   | 11 | 11 | 55  | 55  | 4      |

| Alexnet_CONV2  | 27  | 27  | 256 | 64   | 192  | 5  | 5  | 27  | 27  | 1      |

| Alexnet_CONV3  | 13  | 13  | 256 | 192  | 384  | 3  | 3  | 13  | 13  | 1      |

| Alexnet_CONV4  | 13  | 13  | 256 | 384  | 256  | 3  | 3  | 13  | 13  | 1      |

| Alexnet_CONV5  | 13  | 13  | 256 | 256  | 256  | 3  | 3  | 13  | 13  | 1      |

| Overfeat_CONV1 | 231 | 231 | 256 | 3    | 96   | 11 | 11 | 56  | 56  | 4      |

| Overfeat_CONV2 | 28  | 28  | 256 | 96   | 256  | 5  | 5  | 24  | 24  | 1      |

| Overfeat_CONV3 | 12  | 12  | 256 | 256  | 512  | 3  | 3  | 12  | 12  | 1      |

| Overfeat_CONV4 | 12  | 12  | 256 | 512  | 1024 | 3  | 3  | 12  | 12  | 1      |

| Overfeat_CONV5 | 12  | 12  | 256 | 1024 | 1024 | 3  | 3  | 12  | 12  | 1      |

| Vgga_CONV1     | 224 | 224 | 128 | 3    | 64   | 3  | 3  | 224 | 224 | 1      |

| Vgga_CONV2     | 112 | 112 | 256 | 64   | 128  | 3  | 3  | 112 | 112 | 1      |

| Vgga_CONV3     | 56  | 56  | 256 | 128  | 256  | 3  | 3  | 56  | 56  | 1      |

| Vgga_CONV4     | 56  | 56  | 256 | 256  | 256  | 3  | 3  | 56  | 56  | 1      |

| Vgga_CONV5     | 28  | 28  | 256 | 256  | 512  | 3  | 3  | 28  | 28  | 1      |

| Vgga_CONV6     | 28  | 28  | 256 | 512  | 512  | 3  | 3  | 28  | 28  | 1      |

| Vgga_CONV7     | 14  | 14  | 256 | 512  | 512  | 3  | 3  | 14  | 14  | 1      |

| Vgga_CONV8     | 14  | 14  | 256 | 512  | 512  | 3  | 3  | 14  | 14  | 1      |